一种芯片研磨方法与流程

2021-01-30 07:01:05|

2021-01-30 07:01:05| 279|

279| 起点商标网

起点商标网

[0001]

本发明涉及半导体技术领域,具体涉及一种芯片研磨方法。

背景技术:

[0002]

射频芯片(radiofrequencychip,rf chip)指的就是将无线电信号通信转换成一定的无线电信号波形,并通过天线谐振发送出去的一个电子元器件。在芯片设计上,射频芯片引入了mim(metalisolationmetal)结构,用于形成大的电容结构,对射频信号进行收发,从而实现射频的功能。mim结构是由金属、绝缘体、金属三层薄膜组成的夹心结构。

[0003]

mim结构嵌入至介质层中,且在两个mim结构之间形成附加槽,mim结构上形成连接槽,在进行导电材料沉积后,附加槽内、连接槽内及介质层顶部表面上均形成有导电材料层。随后,需要通过研磨工艺对上述结构进行研磨,以去除附加槽中的导电材料层。一般采用化学机械抛光(chemical mechanical planarization,简称cmp)进行研磨处理。采用化学机械抛光的基本原理是将待抛光工件在一定的下压强及研磨液的存在下,相对于一个抛光垫作旋转运动,借助磨粒的机械磨削及化学氧化剂的腐蚀作用来完成对附加槽内导电材料层的去除,并获得光洁表面。

[0004]

然而,现有的研磨方法造成连接槽内的导电材料层较大程度的损耗。

技术实现要素:

[0005]

因此,本发明要解决的技术问题在于克服现有芯片研磨方法造成连接槽内的导电材料层较大程度的损耗的缺陷,从而提供一种芯片研磨方法。

[0006]

为此,本发明提供一种芯片研磨方法,包括以下步骤:

[0007]

提供待研磨基片,所述研磨基片包括:介质层;位于所述介质层中的连接槽和附加槽;位于所述连接槽和所述附加槽内部、以及所述介质层顶部表面的导电材料层;

[0008]

采用第一研磨工艺研磨去除高于所述介质层顶部表面的所述导电材料层;

[0009]

采用第二研磨工艺研磨位于所述附加槽侧部的介质层,使得附加槽区域的导电材料层凸出于所述介质层;

[0010]

采用第三研磨工艺去除附加槽区域的导电材料层。

[0011]

可选的,所述芯片研磨方法还包括:进行第三研磨工艺之后,采用第四研磨工艺去除所述连接槽两侧的部分厚度的介质层,使得所述连接槽内的导电材料层的顶面与所述介质层的顶面平齐,或,所述连接槽内的导电材料层的顶面高于所述介质层的顶面。

[0012]

可选的,所述第三研磨工艺对待研磨基片施加的研磨压强≤所述第一研磨工艺对待研磨基片施加的研磨压强。

[0013]

可选的,所述第二研磨工艺的研磨速率为研磨时间为60s-300s;

[0014]

所述第三研磨工艺的研磨速率为研磨时间为20s~150s。

[0015]

可选的,所述第一研磨工艺包括依次进行的第一子研磨工艺和第二子研磨工艺,所述第二子研磨工艺的研磨速率小于第一子研磨工艺的研磨速率。

[0016]

可选的,所述第二子研磨工艺中对待研磨基片施加的研磨压强小于第一子研磨工艺对待研磨基片施加的研磨压强。

[0017]

可选的,所述第一子研磨工艺的研磨压强为2.5psi-4psi;所述第二子研磨工艺中施加的研磨压强为1psi-3psi。

[0018]

可选的,所述第一研磨工艺的过研磨时间为5s~50s。

[0019]

可选的,所述芯片研磨方法还包括:在进行所述第一研磨工艺、所述第二研磨工艺及所述第三研磨工艺的过程中,对研磨垫表面的副产物进行清理。

[0020]

可选的,所述研磨基片还包括:位于所述连接槽的侧壁和底面、所述附加槽的侧壁和底面以及介质层顶部表面的阻挡层,且所述导电材料层位于所述阻挡层上;

[0021]

所述第一研磨工艺研磨所述导电材料层直至暴露出所述介质层顶部表面的所述阻挡层;

[0022]

所述第二研磨工艺还去除了所述附加槽侧壁的阻挡层;

[0023]

所述第四研磨工艺还去除了附加槽区域底部的阻挡层。

[0024]

可选的,所述芯片为射频芯片;所述待研磨基片还包括:位于介质层底部的mim结构,所述连接槽位于所述mim结构的上方,所述附加槽位于相邻mim结构之间的介质层顶部区域。

[0025]

本发明技术方案,具有如下优点:

[0026]

1.本发明提供的芯片研磨方法,首先通过第一研磨工艺将高于介质层顶部表面的导电材料层去除,然后通过第二研磨工艺使填充在附加槽内的导电材料层凸出于所述介质层,第二研磨工艺完成之后,连接槽内部的导电材料层的顶部区域也相应的凸出于介质层,随后通过第三研磨工艺去除附加槽区域的导电材料层。由于第三研磨工艺之前,附加槽内的导电材料层凸出于所述介质层,因此第三研磨工艺的过程中,研磨压力能够直接施加在附加槽内的导电材料层上,研磨垫与该导电材料层形成充分的接触,使得第三研磨工艺在去除附加槽内的导电材料层的过程中,化学刻蚀和机械力研磨同时发挥作用,避免了常规研磨方法由于附加槽内的导电材料层与研磨垫无法直接接触导致的机械力研磨作用弱的缺点,提高了附加槽内的导电材料层的研磨速率,且第三研磨工艺能够同时对附加槽内的导电材料层的顶面和侧壁进行研磨,使附加槽内的导电材料层能够比较容易的去除,缩短了附加槽内的导电材料层的研磨时间。由于第三研磨工艺之前,连接槽内部的导电材料层的顶部区域凸出于介质层,因此第三研磨工艺的过程中,研磨压力能够直接施加在连接槽内的导电材料层上,研磨垫与该导电材料层形成充分的接触,使得第三研磨工艺在去除连接槽内的导电材料层的过程中,不仅对连接槽内的导电材料层的顶面还对连接槽内的导电材料层的侧壁进行研磨,使得对于连接槽内的导电材料层边缘区域的研磨速率和中心区域的研磨速率相近,这样避免中心区域相对于边缘区域过多的凹陷。由于去除附加槽内的导电材料层的时间较短,且避免了连接槽内的导电材料层发生凹陷,因此可以降低连接槽内的导电材料层的损耗程度。

[0027]

2.本发明提供的芯片研磨方法,进行第三研磨工艺之后,采用第四研磨工艺去除所述连接槽两侧的部分厚度的介质层,使得所述连接槽内的导电材料层的顶面与所述介质

层的顶面平齐,或,所述连接槽内的导电材料层的顶面高于所述介质层的顶面,使得连接槽内导电材料层与其他待电电学连接的结构之间接触充分,利于连接槽内导电材料层与其他结构电连接,避免引起断路。

[0028]

3.本发明提供的芯片研磨方法,在进行第一研磨工艺的过程中,首先通过第一子研磨工艺以较高的研磨速率去除高于介质层顶部表面导电材料层的大部分厚度,随后第二子研磨工艺以较低的研磨速率去除剩余的高于介质层顶部表面的导电材料层,即,提高了第一研磨工艺的平均研磨速率,从而缩短了第一研磨工艺的研磨时间,提高了研磨效率;同时,第二子研磨工艺较低的研磨速率有利于控制研磨终点。

[0029]

4.本发明提供的芯片研磨方法,通过限定所述第二子研磨工艺中对待研磨基片施加的研磨压强小于第一子研磨工艺对待研磨基片施加的研磨压强,使所述第二子研磨工艺的研磨速率小于第一子研磨工艺的研磨速率;同时,以较高的研磨压强进行第一子研磨工艺使待研磨基片的不同区域具有较小的厚度差异,随后,以较低的研磨压强进行第二子研磨工艺使待研磨基片的研磨表面具有较低的粗糙度,即,第一子研磨工艺与第二子研磨工艺相互配合,得到了具有较高研磨精度和较高平整度的研磨表面,有利于保证后续研磨工艺的研磨效果。

[0030]

5.本发明提供的芯片研磨方法,所述第一研磨工艺过研磨5s~50s可以保证待研磨基片中高于介质层顶部表面各区域内的导电材料层均能完全去除,提高待研磨基片整体的研磨效果和研磨后待研磨基片的平整度。

[0031]

6.本发明提供的芯片研磨方法,在进行所述第一研磨工艺、所述第二研磨工艺及所述第三研磨工艺的过程中,对研磨垫表面的研磨副产物进行清理,保证了研磨速率的稳定性,以避免由于研磨副产物填充研磨垫自身孔洞并沉积在研磨垫表面导致的研磨速率降低和研磨速率不稳定的问题,能够使同一片待研磨基片的厚度差异控制至以内,提高了研磨后待研磨基片的平整度。

[0032]

7.本发明提供的芯片研磨方法,所述第三研磨工艺的研磨压强≤所述第二子研磨工艺的研磨压强。以较低的研磨压强进行第三研磨工艺使连接槽和所述附加槽内部的导电材料层的表面具有较低的粗糙度,并降低连接槽内的导电材料层的损耗程度。

附图说明

[0033]

为了更清楚地说明本发明具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0034]

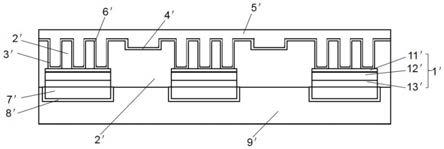

图1和图2为一种芯片研磨过程中的结构示意图;

[0035]

图3为本发明一实施例提供的芯片研磨方法的流程示意图;

[0036]

图4至图9为本发明一实施例提供的芯片研磨过程中的结构示意图。

具体实施方式

[0037]

一种芯片研磨方法,包括:参见图1,提供射频芯片,射频芯片包括:下介质层9

′

、嵌入至下介质层9

′

中的若干下导电材料层7

′

、设置于下介质层9

′

与下导电材料层7

′

之间的下

阻挡层8

′

、设置于下导电材料层7

′

上的mim结构1

′

和介质层2

′

、位于mim结构1

′

上的连接槽3

′

、位于相邻mim结构1

′

之间的附加槽4

′

、位于连接槽3

′

和附加槽4

′

内部以及介质层2

′

顶部表面的导电材料层5

′

,mim结构1

′

包括层叠设置的导电上极板11

′

、中部介质层12

′

和导电下极板13

′

;参考图2,以一定的研磨速率对导电材料层进行研磨,待去除高于介质层顶部表面的导电材料层后,继续研磨一定时间,以完全去除射频芯片中附加槽内的导电材料层。

[0038]

在射频芯片的制备过程中,首先在下导电材料层7

′

上形成mim结构1

′

,相邻的mim结构1

′

之间具有凹槽,从而造成在后续介质层沉积后,在两mim结构1

′

之间形成位于介质层顶部区域的附加槽4

′

,继而在沉积导电材料层后,附加槽内也填充有导电材料层。

[0039]

研究发现,由于介质层与导电材料层的材质不同,在附加槽内的导电材料层被研磨的过程中,介质层的研磨速率远小于导电材料层的研磨速率,甚至介质层基本未被研磨,使附加槽内的导电材料层不与其邻近的介质层表面平齐,由于介质层的阻挡,导致附加槽内的导电材料层与研磨垫无法保持有效接触,具体的,当附加槽内的导电材料层的中心区域研磨完成之后,附加槽内的导电材料层的边缘区域还具有一定的残留,为了保证附加槽内的导电材料层能够完全去除,势必就要延长研磨时间,对附加槽内的导电材料层的研磨时间也相应比较长。其次,在附加槽内的导电材料层研磨的过程中,连接槽内的部分导电材料层也一同被研磨,当附加槽内的导电材料层被完全去除时,连接槽内的导电材料层由于dishing缺陷形成较深的凹槽。较长的研磨时间和连接槽内的导电材料层的dishing缺陷造成连接槽内的导电材料层较大程度的损耗。

[0040]

在此基础上,本发明提供一种芯片研磨方法,参考图3,包括以下步骤:

[0041]

s1:提供待研磨基片,研磨基片包括:介质层;位于介质层中的连接槽和附加槽;位于连接槽内部、附加槽内部以及介质层顶部表面的导电材料层;

[0042]

s2:采用第一研磨工艺研磨去除高于介质层顶部表面的导电材料层;

[0043]

s3:采用第二研磨工艺研磨位于附加槽侧部的介质层,使得附加槽的区域的导电材料层凸出于介质层;

[0044]

s4:采用第三研磨工艺去除附加槽的区域的导电材料层。

[0045]

上述芯片研磨方法,首先通过第一研磨工艺将高于介质层顶部表面的导电材料层去除,然后通过第二研磨工艺使填充在附加槽内的导电材料层凸出于介质层,第二研磨工艺完成之后,连接槽内部的导电材料层的顶部区域也相应的凸出于介质层,随后通过第三研磨工艺去除附加槽区域的导电材料层。由于第三研磨工艺之前,附加槽内的导电材料层凸出于介质层,因此第三研磨工艺的过程中,研磨压力能够直接施加在附加槽内的导电材料层上,研磨垫与该导电材料层形成充分的接触,使得第三研磨工艺在去除附加槽内的导电材料层的过程中,化学刻蚀和机械力研磨同时发挥作用,避免了常规研磨方法由于附加槽内的导电材料层与研磨垫无法直接接触导致的机械力研磨作用弱的缺点,提高了附加槽内的导电材料层的研磨速率,且第三研磨工艺能够同时对附加槽内的导电材料层的顶面和侧壁进行研磨,使附加槽内的导电材料层能够比较容易的去除,缩短了附加槽内的导电材料层的研磨时间。由于第三研磨工艺之前,连接槽内部的导电材料层的顶部区域凸出于介质层,因此第三研磨工艺的过程中,研磨压力能够直接施加在连接槽内的导电材料层上,研磨垫与该导电材料层形成充分的接触,使得第三研磨工艺在去除连接槽内的导电材料层的过程中,不仅对连接槽内的导电材料层的顶面还对连接槽内的导电材料层的侧壁进行研

磨,使得对于连接槽内的导电材料层边缘区域的研磨速率和中心区域的研磨速率相近,这样避免中心区域相对于边缘区域过多的凹陷。由于去除附加槽内的导电材料层的时间较短,且避免了连接槽内的导电材料层发生凹陷,因此可以降低连接槽内的导电材料层的损耗程度。

[0046]

下面参考图4至图9,具体详细的介绍本发明实施例提供的芯片研磨过程。

[0047]

参考图5,提供待研磨基片。待研磨基片包括:介质层2;位于介质层2中的连接槽3(参考图4)和附加槽4(参考图4);位于连接槽内部、附加槽内部以及介质层顶部表面的导电材料层5。

[0048]

待研磨基片的形成过程包括:参考图4,形成介质层2及位于介质层2中的连接槽3和附加槽4;参考图5,形成位于连接槽内部、附加槽内部以及介质层顶部表面的导电材料层5。

[0049]

本实施例的芯片为射频芯片;待研磨基片还包括:位于介质层2底部的mim结构1,连接槽3位于mim结构1的上方,附加槽4位于相邻mim结构1之间的介质层顶部区域。

[0050]

具体的,待研磨基片的结构包括以下结构:

[0051]

下介质层9;

[0052]

若干下导电材料层7,下导电材料层7嵌入至下介质层9;

[0053]

下阻挡层8,设置于下介质层9与下导电材料层7之间;

[0054]

mim结构1,设置于下导电材料层7上,mim结构1包括层叠设置的导电上极板11、中部介质层12和导电下极板13。

[0055]

介质层2,设置于下导电材料层7上,且mim结构1嵌入至介质层2中,介质层2的材质包括但不限于sio

2

、sioc、sion。

[0056]

连接槽3,位于介质层2中,并位于mim结构1上;

[0057]

附加槽4,位于介质层2中,并位于两相邻mim结构1之间,且附加槽4的深度小于连接槽3。

[0058]

导电材料层5,位于连接槽3内部、附加槽4内部以及介质层2顶部表面,导电材料层5的材质包括但不限于铜。

[0059]

此外,研磨基片还可以包括:位于连接槽3的侧壁和底面、附加槽4的侧壁和底面以及介质层2顶部表面的阻挡层6,且导电材料层5位于阻挡层6上,阻挡层6的材质包括但不限于ta、tan、co、tin。

[0060]

参考图6,采用第一研磨工艺研磨去除高于介质层2顶部表面的导电材料层5。当研磨基片还包括阻挡层6时,第一研磨工艺研磨导电材料层直至暴露出介质层顶部表面的阻挡层。

[0061]

第一研磨工艺采用终点检测方法获得介质层顶部表面的导电材料层的研磨终点,研磨至研磨终点后继续研磨5s~50s。终点检测方法可以对介质层顶部表面某一区域的研磨程度进行检测,以判断该区域内的导电材料层是否完全去除,待完全去除时即为研磨终点,研磨至研磨终点后继续研磨5s~50s可以保证待研磨基片中介质层顶部表面各区域内的导电材料层均能完全去除,提高待研磨基片整体的研磨效果和研磨后待研磨基片的平整度。在一些具体的实施例中,过研磨时间可以为5s、10s、15s、20s、25s、30s、35s、40s、45s、50s,终点检测方法采用电机电流终点检测、电涡流终点检测、综合终点检测方法中的其中

一种。

[0062]

第一研磨工艺的参数包括:研磨压强为1psi-3psi,研磨盘和研磨头的相对转速为2转/min~10转/min,其中研磨盘的转速为80转/min~120转/min,研磨头的转速为80转/min~120转/min,研磨盘与研磨头的转动方向相同;在一些具体的实施例中,第一研磨工艺可以用以下参数进行:研磨盘的转速为93转/min,研磨头的转速为87转/min,研磨压强为2.5psi的压力。

[0063]

作为一种优选的实施方式,第一研磨工艺包括依次进行的第一子研磨工艺和第二子研磨工艺,第二子研磨工艺的研磨速率小于第一子研磨工艺的研磨速率。即,首先通过第一子研磨工艺以较高的研磨速率去除介质层顶部表面导电材料层的大部分厚度,随后第二子研磨工艺以较低的研磨速率去除剩余的介质层顶部表面的导电材料层,提高了第一研磨工艺的平均研磨速率,从而缩短了第一研磨工艺的研磨时间,提高了研磨效率;同时,第二子研磨工艺较低的研磨速率有利于控制研磨终点,从而避免过抛程度过大。具体的,第一子研磨工艺研磨掉介质层顶部表面的导电材料层的总厚度的85%,当介质层顶部表面的导电材料层的总厚度为时,第一子研磨工艺研磨掉第二子研磨工艺研磨掉剩余的

[0064]

第一子研磨工艺与第二子研磨工艺中的研磨盘和研磨头的相对转速相同,第二子研磨工艺中对待研磨基片施加的研磨压强小于第一子研磨工艺对待研磨基片施加的研磨压强,使得第二子研磨工艺的研磨速率小于第一子研磨工艺的研磨速率;同时,对待研磨基片以较高的研磨压强进行第一子研磨工艺使待研磨基片的不同区域具有较小的厚度差异,以较低的研磨压强进行第二子研磨工艺使待研磨基片的研磨表面具有较低的粗糙度,即,第一子研磨工艺与第二子研磨工艺相互配合,得到了具有较高研磨精度和较高平整度的研磨表面,有利于保证后续研磨工艺的研磨效果。

[0065]

进一步地,第一子研磨工艺的研磨压强为2.5psi-4psi,第二子研磨工艺中施加的研磨压强为1psi-3psi,第一子研磨工艺与第二子研磨工艺中研磨盘和研磨头的相对转速为2转/min~10转/min,其中研磨盘的转速为80转/min~120转/min,研磨头的转速为80转/min~120转/min,研磨盘与研磨头的转动方向相同。在一些具体的实施例中,第一子研磨工艺与第二子研磨工艺中,研磨盘的转速为93转/min,研磨头的转速为87转/min,第一子研磨工艺的研磨压强为3.5psi,第二子研磨工艺的研磨压强为2.5psi。

[0066]

当导电材料层5为金属时,第一子研磨工艺可以通过电磁终点检测系统监控研磨终点;第二子研磨工艺可以通过光学终点检测、电机电流终点检测、电涡流终点检测、综合终点检测方法中的其中一种监控研磨终点,当导电材料层5为金属时,第二子研磨工艺通过光学终点检测监控研磨终点结果更为准确。

[0067]

此外,在进行第一研磨工艺的过程中,还包括对研磨垫表面的研磨副产物进行清理的步骤。通过对副产物的清理,保证了研磨速率的稳定性,以避免由于研磨副产物填充研磨垫自身孔洞并沉积在研磨垫表面导致的研磨速率降低和研磨速率不稳定的问题,能够使同一片待研磨基片的厚度差异控制至以内,提高了研磨后待研磨基片的平整度。具体的,第一研磨工艺可使用硬度较低的无纺布抛光垫,搭配毛刷在研磨之前对抛光垫进行梳理(exsitu,预先梳理),同时每研磨30s-60s用高压水冲洗研磨垫10s~30s。

[0068]

参考图7,采用第二研磨工艺研磨位于附加槽4侧部的介质层2,使得附加槽区域的导电材料层5凸出于介质层2。当研磨基片还包括阻挡层6时,第二研磨工艺还去除了附加槽侧壁的阻挡层。

[0069]

第二研磨工艺的研磨速率为第二研磨工艺的研磨时间为60s-300s。根据附加槽4的深度及第二研磨工艺的预设研磨速率可以得出第二研磨工艺的预设研磨时间,然后以第二研磨工艺的预设研磨速率进行研磨并计时,当实际研磨时间等于预设研磨时间时停止研磨。

[0070]

进一步地,第二研磨工艺的参数包括:研磨压强为1psi-3psi,研磨盘和研磨头的相对转速为2转/min~10转/min,其中研磨盘的转速为80转/min~120转/min,研磨头的转速为80转/min~120转/min,研磨盘与研磨头的转动方向相同。

[0071]

此外,在进行第二研磨工艺的过程中,还包括对研磨垫表面的研磨副产物进行清理的步骤。通过对副产物的清理,保证了研磨速率的稳定性,以避免由于研磨副产物填充研磨垫自身孔洞并沉积在研磨垫表面导致的研磨速率降低和研磨速率不稳定的问题,能够使同一片待研磨基片的厚度差异控制至以内,提高了研磨后待研磨基片的平整度。具体的,第二研磨工艺可使用硬度稍高的聚氨酯研磨垫,将上述研磨垫置于金刚石研磨盘上,使用机台上配制的梳理工具在研磨的同时进行梳理(insitu,同步梳理),同时每研磨30s-60s用高压水冲洗研磨垫10s~30s。

[0072]

参考图8,采用第三研磨工艺去除附加槽4区域的导电材料层5。当研磨基片还包括阻挡层6时,第三研磨工艺研磨导电材料层直至暴露附加槽区域底部的阻挡层。

[0073]

第三研磨工艺的研磨速率为第三研磨工艺的研磨时间为20s~150s。根据附加槽内的导电材料层5的深度和第三研磨工艺的预设研磨速率可以得出第三研磨工艺的预设研磨时间,然后以第三研磨工艺的预设研磨速率进行研磨并计时,当实际研磨时间等于预设研磨时间时停止研磨。

[0074]

此外,第三研磨工艺对待研磨基片施加的研磨压强≤第一研磨工艺对待研磨基片施加的研磨压强。具体的,第三研磨工艺对待研磨基片施加的研磨压强≤第二子研磨工艺对待研磨基片施加的研磨压强。以较低的研磨压强进行第三研磨工艺使连接槽3内部和附加槽4内部的导电材料层5的表面具有较低的粗糙度,并降低连接槽3内的导电材料层5的损耗程度。

[0075]

进一步地,第三研磨工艺的参数包括:研磨压强为1psi-3psi,研磨盘和研磨头的相对转速为2转/min~10转/min,其中研磨盘的转速为80转/min~120转/min,研磨头的转速为80转/min~120转/min,研磨盘与研磨头的转动方向相同。在一些具体的实施例中,第三研磨工艺的参数包括:研磨盘的转速为93转/min,研磨头的转速为87转/min,研磨压强为2.5psi的压力。

[0076]

此外,在进行第三研磨工艺的过程中,还包括对研磨垫表面的研磨副产物进行清理的步骤。通过对副产物的清理,保证了研磨速率的稳定性,以避免由于研磨副产物填充研磨垫自身孔洞并沉积在研磨垫表面导致的研磨速率降低和研磨速率不稳定的问题,能够使同一片待研磨基片的厚度差异控制至以内,提高了研磨后待研磨基片的平整度。具体的,第三研磨工艺可使用硬度较低的无纺布抛光垫,搭配毛刷在研磨之前对抛光垫进行

梳理(exsitu,预先梳理),同时每研磨30s-60s用高压水冲洗研磨垫10s~30s。

[0077]

参考图9,本实施例提供的芯片研磨方法还包括:在进行第三研磨工艺之后,采用第四研磨工艺去除连接槽两侧的部分厚度的介质层2,使得连接槽3内的导电材料层5的顶面高于介质层2的顶面,从而使连接槽内的导电材料层与其他待电电学连接的结构之间接触充分,利于连接槽内导电材料层与其他结构电连接,避免引起断路。当研磨基片还包括阻挡层6时,第四研磨工艺还去除了附加槽区域底部的阻挡层。

[0078]

需要理解的是,第四研磨工艺也可以使得连接槽内的导电材料层的顶面与介质层的顶面平齐,从而使连接槽内的导电材料层5与其他待电电学连接的结构之间接触充分,利于连接槽内导电材料层与其他结构电连接,避免引起断路。

[0079]

第四研磨工艺的研磨速率为第四研磨工艺的研磨时间为60s~150s,对介质层2的研磨厚度为根据介质层的预设研磨厚度和第四研磨工艺的预设研磨速率可以得出第四研磨工艺的预设研磨时间,然后以第四研磨工艺的预设研磨速率进行研磨并计时,当实际研磨时间等于预设研磨时间时停止研磨。在一些具体的实施方式中,第四研磨工艺对介质层2的研磨厚度为

[0080]

进一步地,第四研磨工艺的参数包括:研磨压强为1psi-3psi,研磨盘和研磨头的相对转速为2转/min~10转/min,其中研磨盘的转速为80转/min~120转/min,研磨头的转速为80转/min~120转/min,研磨盘与研磨头的转动方向相同。

[0081]

此外,在进行第四研磨工艺的过程中,还包括对研磨垫表面的研磨副产物进行清理的步骤。通过对副产物的清理,保证了研磨速率的稳定性,以避免由于研磨副产物填充研磨垫自身孔洞并沉积在研磨垫表面导致的研磨速率降低和研磨速率不稳定的问题,能够使同一片待研磨基片的厚度差异控制至以内,提高了研磨后待研磨基片的平整度。具体的,第四研磨工艺可使用硬度稍高的聚氨酯研磨垫,将上述研磨垫置于金刚石研磨盘上,使用机台上配制的梳理工具在研磨的同时进行梳理(insitu,同步梳理),同时每研磨30s-60s用高压水冲洗研磨垫10s~30s。

[0082]

在其他实施例中,可以不进行第四研磨工艺。

[0083]

需要理解的是,本实施例提供的研磨方法不仅适用于射频芯片,其他类型或结构的芯片也可使用上述研磨方法。

[0084]

显然,上述实施例仅仅是为清楚地说明所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引伸出的显而易见的变化或变动仍处于本发明创造的保护范围之中。

起点商标作为专业知识产权交易平台,可以帮助大家解决很多问题,如果大家想要了解更多知产交易信息请点击 【在线咨询】或添加微信 【19522093243】 与客服一对一沟通,为大家解决相关问题。

与客服一对一沟通,为大家解决相关问题。

此文章来源于网络,如有侵权,请联系删除

相关标签: 芯片

热门咨询

热门咨询

tips

商标分类

商标分类  商标转让

商标转让