一种降低音频编码器码率的方法、装置及存储介质与流程

2021-01-28 12:01:47|

2021-01-28 12:01:47| 295|

295| 起点商标网

起点商标网

[0001]

本申请涉及无线通信技术领域,尤其涉及一种降低音频编码器码率的方法、装置及存储介质。

背景技术:

[0002]

目前主流的蓝牙音频编码器有如下几种:

[0003]

sbc:蓝牙音频的标准编码格式,a2dp协议强制规定的编码格式,使用最为广泛,是所有的蓝牙音频设备必须支持的,但音质一般;

[0004]

aac-lc:是一种高压缩比的编码算法,音质较好且应用较为广泛,很多主流的手机都支持,但与sbc相比,内存占用较大,且运算复杂度高,很多蓝牙设备都基于嵌入式平台,电池容量有限,处理器运算能力较差且内存有限;

[0005]

aptx系列:声音保留的细节更多,实际听感好于前面两者,这种音频编码技术比传统蓝牙编码效率更高,aptx需要码率384kbps,而aptx-hd的码率为576kbps,且为高通独有的技术,采用aptx技术的设备,需要向高通申请授权并交纳授权费,并且需要发射接收端都支持才行;

[0006]

ldac:音质较好,但码率也很高,分别是330kbps,660kbps和990kbps,由于蓝牙设备所处的无线环境特别复杂,稳定支持如此高的码率有一定的困难,且为sony公司自己开发的一种音频编码技术,目前这种技术只用在sony自己的发射和接收设备上。因此,只有买了sony成套的支持ldac音频编码技术的发射和接受设备,才能够支持ldac编码的蓝牙音频数据传输;

[0007]

lc3:功耗低、延迟较低、音质和编码增益较高,且在蓝牙领域无专利费,相较于前四种编码器,优势诸多,因此lc3受到广大厂商的关注。

[0008]

lc3与现有的cvsd和wbs相比,在相同的采样率下降低了码率,同时提升了音质,但由于基于波形编码技术,与传统的声码器相比,压缩效率很低,举例来说,lc3在8k采样率时的推荐码率为28kbps,但应用于wcdma的amr-nb最大码率仅为12.2kbps,平均码率10kbps以下,应用于cdma系统的evrc-a最大码率为8kbps,平均码率约为5kbps,而3gpp release12推出的应用于volte的evs,其最低码率为5.9kbps。较高的码率占用了较大的带宽,需要更多的发射功率,在公共场合,蓝牙设备较多,相互之间会造成干扰,影响了用户体验,相互干扰的程度与占用的带宽、发射功率有很大关系。

[0009]

基于通话的特性,通常情况下通话的一方只有部分时间在讲话,据统计,通话的一方通常只有约35%的时间在讲话,而目前标准规范的lc3使用固定码率,即开始编码后每一帧语音都是用相同的可用比特数,这就导致一方不说话时仍然使用相同码率编码,造成浪费。

[0010]

在现有技术中,为了节省码率,如前文所述的3gpp和3gpp2中的声码器,都采用了非常复杂的话音激活检测和码率判决算法,虽然可以极大限度的节省码率,但资源消耗都比较大,如代码空间、数据空间以及运算资源。这些方法对于面向低功耗蓝牙平台都不适

用,因为低功耗蓝牙平台字节数和运算能力都较为有限。

[0011]

对于话音帧(通常话音激活检测结果为1),其主要的编码比特用来编码辅助信息和算术编码,剩余少量的编码比特用来对残差信号进行编码。

[0012]

对于非话音帧(话音激活检测结果为0),譬如静音帧或能量很小的噪声,在编码完成辅助信息编码后,算术编码和残差编码只需要极少的编码比特,所以一帧编码结束后会剩余很多比特,在目前的lc3标准规范中,这些剩余的比特数会被填充为0并发送到解码器,造成了带宽资源的浪费。

技术实现要素:

[0013]

本申请针对目前符合标准规范的lc3编码器效率不高的问题,特别是上述的编码比特浪费的问题,提供一种降低音频编码器码率的方法、装置及存储介质,通过降低语音通话时的码率,从而可以节省空中带宽。

[0014]

为实现上述目的,本申请采用的一个技术方案是:提供一种降低音频编码器码率的方法,其包括:判断步骤,对音频编码器中的至少一帧数据所占用的原始字节数是否有冗余进行判断;重新计算步骤,若至少一帧数据所占用的原始字节数有冗余,则对原始字节数有冗余的数据的有效值所实际占用的字节数重新进行计算;以及调整步骤,根据至少一帧数据的有效值所实际占用的字节数,对至少一帧数据重新分配其所需的字节数。

[0015]

本申请采用另一个技术方案是:提供一种降低音频编码器码率的装置,其包括:判断模块,用于对音频编码器中的至少一帧数据所占用的原始字节数是否有冗余进行判断的模块;重新计算模块,用于若至少一帧数据所占用的原始字节数有冗余,则对原始字节数有冗余的数据的有效值所实际占用的字节数重新进行计算的模块;以及调整模块,用于根据至少一帧数据的有效值所实际占用的字节数,对至少一帧数据重新分配其所需的字节数的模块。

[0016]

本申请采用另一个技术方案是:提供一种计算机可读存储介质,其中计算机可读存储介质中存储有计算机执行指令,计算机执行指令被处理器执行时可实现方案一中的降低音频编码器码率的方法。

[0017]

本申请采用另一个技术方案是:提供一种计算机设备,其包括处理器和存储器,存储器存储有计算机指令,其中处理器操作计算机指令以执行时可实现方案一中的降低音频编码器码率的方法。

[0018]

本申请的有益效果是:提供一种降低音频编码器码率的方法、装置及存储介质,通过调整每帧输出的编码比特流,在确保编码结果不变的前提下,有效的降低码率,从而可用节省空中带宽。

附图说明

[0019]

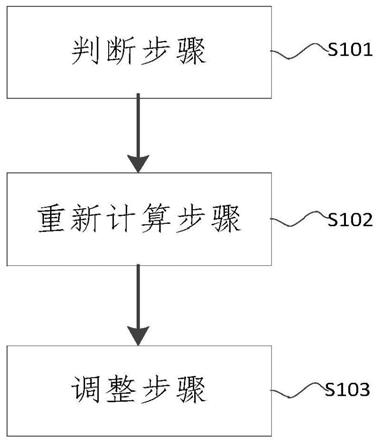

图1是本申请的一种降低音频编码器码率方法的一个具体实施方式的流程示意图;

[0020]

图2是本申请的音频编码器当前帧按照标准编码输出的码流的一个具体实施例的示意图;

[0021]

图3是本申请的音频编码器当前帧降低码率之后输出的码流的一个具体实施例的

示意图;

[0022]

图4是本申请的音频编码器编码模块的一个具体实施方式的示意图;

[0023]

图5是本申请的一种降低音频编码器码率装置的一个具体实施方式的流程示意图。

具体实施方式

[0024]

下面结合附图对本申请的较佳实施例进行详细阐述,以使本申请的优点和特征能更易于被本领域技术人员理解,从而对本申请的保护范围做出更为清楚明确的界定。

[0025]

需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

[0026]

本申请所使用的音频编码器在编码的过程中,对于辅助信息编码、算术编码和残差编码均按照标准规范完成,此处不再赘述。

[0027]

图1的流程示意图示出了本申请一种降低音频编码器码率的方法的一个具体实施方式。

[0028]

在图1所示的具体实施方式中,本申请的降低音频编码器码率的方法包括过程s101、过程s102以及过程s103。

[0029]

图1所示的过程s101为判断步骤:对音频编码器中的至少一帧数据所占用的原始字节数是否有冗余进行判断。

[0030]

在本申请的一个具体实施例中,以lc3编码器为例,对于计算音频编码器中的每一帧数据所占用的原始字节数冗余的过程,利用音频编码器当前帧数据可用的总字节数减去辅助信息编码、算数编码以及残差信息编码已占用的字节数,剩下的即为音频编码器当前帧数据所占用的原始字节数的冗余。在本实施例中,若音频编码器当前帧数据所占用的原始字节数有冗余,则说明音频编码器当前帧数据所占用的原始字节数存在带宽浪费现象,若音频编码器当前帧所占用的原始字节数无冗余,则按照标准规范进行下一步操作即可。

[0031]

在本申请的一个具体实例中,nbits为当前帧可用的总比特数,nbits_side是当前帧已用的辅助信息编码的比特数,nbits_residual_enc是当前帧已用的残差信息编码的比特数,nbits_ari是当前帧已用的算术编码的比特数saved_bits是当前帧数据可以节省的比特数,saved_bytes是当前帧可以节省的字节数;下述

‘8’

指的是保护比特数,如果某个部分的比特数不是8的整数倍,右移3位后则会丢失一部分;因此,所以需要保护。此处简便起见,各个模块的输出比特数都增加了保护;即可得出音频编码器当前帧可以节省的比特数为:saved_bytes=(nbits>>3)

–

((nbits_side+8)>>3)

–

((nbits_ari+8)>>3)

–

((nbits_residual_enc+8)>>3)。

[0032]

图1所示的过程s102为重新计算步骤:若至少一帧数据所占用的原始字节数有冗余,则对原始字节数有冗余的数据的有效值所实际占用的字节数重新进行计算。

[0033]

在本申请的一个具体实施例中,音频编码器中有冗余的帧数据的有效值所占用的字节数为音频编码器当前帧数据所占用的原始字节数的总字节数减去音频编码器当前帧数据所占用的原始字节数冗余的字节数。当前步骤为下一步对原始字节数冗余的帧数据重新分配字节数作准备。

[0034]

在本申请的一个具体实例中,优先的,在帧长为10ms,采样率为16k,码率为64kbps的lc3音频编码器中;nbytes为80,即每帧输出的字节数为80。音频编码器当前帧需要输出的字节数为:nbytes=nbytes

–

saved_bytes。

[0035]

图1所示的过程s103为调整步骤:根据至少一帧数据的有效值所实际占用的字节数,对至少一帧数据重新分配其所需的字节数。

[0036]

在本申请的一个具体实施例中,若任一帧数据的有效值所实际占用的字节数小于音频编码器标准规定的一帧编码最小需要的字节数,则对数据重新分配的字节数为编码器标准规定的所述字节数。

[0037]

在本申请的一个具体实例中,优先的,标准规定一帧编码最小需要的字节数为20;因此,对有效值所实际占用的字节数小于音频编码器标准规定的一帧编码最小需要的字节数的帧数据重新分配20个字节的存储空间。图2是按照标准编码输出的码流,共占据80个字节,可以看出前面大部分数据都是0,浪费了宝贵的带宽;图3是按照本申请输出的码流,共占据20个字节,节省了60个字节。

[0038]

在本申请的一个具体实施例中,若任一帧数据的有效值所实际占用的字节数不小于音频编码器标准规定的一帧编码最小需要的字节数,则对数据重新分配的字节数为其有效值所实际占用的字节数。当前步骤有效利用当前帧数据的码率,节省音频编码器当前帧未使用的原始字节数的字节数,节省空中带宽。

[0039]

在本申请的一个具体实施例中,调整步骤包括:从音频编码器中的至少一帧数据所占用的原始字节数中将算术编码的数据和辅助信息的数据与残差信息的数据分别进行拷贝;以及将拷贝的算术编码的数据、辅助信息的数据以及残差信息的数据分别放入对其重新分配的字节数中。实现对当前帧数据所需字节数的有效利用。

[0040]

在本申请的一个具体实施例中,从音频编码器中的至少一帧数据所占用的原始字节数中将算术编码的数据进行拷贝的过程包括:对音频编码器中的至少一帧数据中的算术编码的数据的长度进行计算,并记录算数编码的数据的起始点。

[0041]

在本申请的一个具体实例中,优先的,在帧长为10ms,采样率为16k,码率为64kbps的lc3音频编码器中;计算第一拷贝长度copy_length1和第一拷贝起始点copy_start1,其对应算术编码的数据长度,并从原始字节数起始点拷贝算术编码到新字节数;其操作步骤为:

[0042]

copy_length1=((nbits_ari+8)>>3);

[0043]

copy_start1=0;

[0044]

在本申请的一个具体实施例中,从音频编码器中的至少一帧数据所占用的原始字节数中将辅助信息的数据与残差信息的数据进行拷贝的过程包括:对音频编码器中的至少一帧数据中的辅助信息的数据与残差信息的数据的长度进行计算,并记录所述辅助信息的数据与残差信息的数据的起始点。

[0045]

在本申请的一个具体实例中,优先的,在帧长为10ms,采样率为16k,码率为64kbps

的lc3音频编码器中;计算第二拷贝长度copy_length2和第二拷贝起始点copy_start2,其对应辅助信息的数据和残差信息的数据;其操作步骤为:copy_length2=((nbits_side+8)>>3)+((nbits_residual_enc+8)>>3);copy_start2=(nbits>>3)-copy_length2;

[0046]

在上述步骤进行完之后,继续按照lc3编解码标准规范相关要求进行下一步的操作。在完成本申请的相关步骤之后,音频编码器编码的新的整体操作流程图如图4所示;编码过程中减小了数据帧的字节数,从而降低了码率,解决了空中带宽浪费的情况。

[0047]

图5的流程示意图示出了本申请一种降低音频编码器码率的装置的一个具体实施方式。

[0048]

在图5所示的具体实施方式中,本申请的降低音频编码器码率的装置包括:模块501、模块502以及模块503。

[0049]

图5所示的模块501为判断模块:用于对音频编码器中的至少一帧数据所占用的原始字节数是否有冗余进行判断的模块。图5所示的模块502为重新计算模块:用于若至少一帧数据所占用的原始字节数有冗余,则对原始字节数有冗余的数据的有效值所实际占用的字节数重新进行计算的模块。图5所示的模块503为调整模块:用于根据至少一帧数据的有效值所实际占用的字节数,对至少一帧数据重新分配其所需的字节数的模块。

[0050]

在本申请的一个具体实施方式中,本申请的降低音频编码器码率的装置中的模块501、模块502以及模块503,可直接在硬件中、在由处理器执行的软件模块中或在两者的组合中。

[0051]

软件模块可驻留在ram存储器、快闪存储器、rom存储器、eprom存储器、eeprom存储器、寄存器、硬盘、可装卸盘、cd-rom或此项技术中已知的任何其它形式的存储介质中。示范性存储介质耦合到处理器,使得处理器可从存储介质读取信息和向存储介质写入信息。

[0052]

处理器可以是中央处理单元(英文:central processing unit,简称:cpu),还可以是其他通用处理器、数字信号处理器(英文:digital signal processor,简称:dsp)、专用集成电路(英文:application specific integrated circuit,简称:asic)、现场可编程门阵列(英文:field programmable gate array,简称:fpga)或其它可编程逻辑装置、离散门或晶体管逻辑、离散硬件组件或其任何组合等。通用处理器可以是微处理器,但在替代方案中,处理器可以是任何常规处理器、控制器、微控制器或状态机。处理器还可实施为计算装置的组合,例如dsp与微处理器的组合、多个微处理器、结合dsp核心的一个或一个以上微处理器或任何其它此类配置。在替代方案中,存储介质可与处理器成一体式。处理器和存储介质可驻留在asic中。asic可驻留在用户终端中。在替代方案中,处理器和存储介质可作为离散组件驻留在用户终端中。

[0053]

本申请的一种优化音视频编解码器内存的装置,可用于执行上述任一实施例描述的降低音频编码器码率的方法,其实现原理和技术效果类似,在此不再赘述。

[0054]

在本申请的一个具体实施方式中,一种计算机可读存储介质,其存储有计算机指令,计算机指令被操作以执行任一实施例描述的一种降低音频编码器码率的方法。

[0055]

在本申请的一个具体实施方式中,一种计算机设备,其包括处理器和存储器,存储器存储有计算机指令,其中,处理器操作计算机指令以执行任一实施例描述的一种降低音频编码器码率的方法。

[0056]

本申请对于lc3语音编码有较好的效果,对于本申请开始所示的测试向量可以将

其平均码率从64kbps降低至42.6kbps,且音质完全一样。

[0057]

本申请以语音编码举例,其原理可以应用于10毫秒帧长和7.5毫秒帧长的语音编码,以及所有的采样率;也可以用于10毫秒帧长和7.5毫秒帧长的音乐编码,以及所有的采样率。本申请带来的有益效果是,降低语音通话时的码率,从而可节省空中带宽;本申请的实现非常简单,只需要增加少量的控制代码用来更新码率。

[0058]

在本申请所提供的实施方式中,应该理解到,所揭露的装置和方法,可以通过其它的方式实现。例如,以上所描述的装置实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或单元的间接耦合或通信连接,可以是电性,机械或其它的形式。

[0059]

所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

[0060]

以上所述仅为本申请的实施例,并非因此限制本申请的专利范围,凡是利用本申请说明书及附图内容所作的等效结构变换,或直接或间接运用在其他相关的技术领域,均同理包括在本申请的专利保护范围内。

起点商标作为专业知识产权交易平台,可以帮助大家解决很多问题,如果大家想要了解更多知产交易信息请点击 【在线咨询】或添加微信 【19522093243】 与客服一对一沟通,为大家解决相关问题。

与客服一对一沟通,为大家解决相关问题。

此文章来源于网络,如有侵权,请联系删除

热门咨询

热门咨询

tips

商标分类

商标分类  商标转让

商标转让