阵列基板行驱动电路及显示装置的制作方法

2021-01-25 12:01:59|

2021-01-25 12:01:59| 254|

254| 起点商标网

起点商标网

[0001]

本揭示涉及显示技术领域,具体涉及一种阵列基板行驱动电路及显示装置。

背景技术:

[0002]

阵列基板行驱动(goa,gate-driver on array)电路基板中q(n)电位在预充电阶段的有效抬升可保证电路的正常输出。由于其中薄膜晶体管(tft,thin film transistor)器件在开态至关态转变时,存在一定的弛豫时间,在此期间,tft并未彻底关闭,就会造成goa电路中q(n)与其相关的tft器件形成漏电通道,从而影响q(n)电位的有效抬升。

[0003]

故,有需要提供一种提高q点预充电能力的阵列基板行驱动电路及显示装置,以解决现有技术存在的问题。

技术实现要素:

[0004]

为解决上述问题,本揭示提出一种阵列基板行驱动电路及其显示装置,从而改善由于与第n级栅极信号点连接的晶体管在预充电阶段关闭不够彻底,而导致阵列基板行驱动电路在预充电阶段漏电的问题。

[0005]

为达成上述目的,本揭示提供一种阵列基板行驱动电路,包括:上拉控制模块,所述上拉控制模块配置为接收第n-4级输出信号及第n-4级时脉信号,所述上拉控制模块与第n级栅极信号点连接,所述第n级栅极信号点配置为输出第n级栅极信号;级传模块,所述级传模块配置为接收第一时脉信号,与第一输出信号及第二输出信号连接;上拉模块,与所述级传模块及第n级水平扫描信号连接;结构反馈信号模块,配置为分别与所述第一输出信号、所述第二输出信号及所述上拉控制模块连接;下拉模块,与第二恒压低电位、所述第n级水平扫描信号以及第n+4级输出信号连接;下拉维持模块,与所述上拉控制模块、所述下拉模块、第一恒压低电位、所述第二恒压低电位以及所述第n级栅极信号点连接;反相器,与恒压高电位、所述下拉维持模块、所述第n级栅极信号点及所述下拉模块连接,所述反相器在第n级反相栅极信号点输出第n级反相栅极信号;以及下拉维持栅极控制模块,电连接在所述下拉维持模块与反相器之间,所述下拉维持栅极控制模块根据第n级栅极反相信号及第n-4级输出信号开启或关闭。

[0006]

于本揭示其中的一实施例中,所述上拉控制模块包括第一上拉控制晶体管及第二上拉控制晶体管,所述第一上拉控制晶体管的第一端配置为接收第n-4级输出信号,所述第一上拉控制晶体管的栅极配置为连接第n-4级时脉信号,所述第一上拉控制晶体管的第二端与所述第二上拉控制晶体管的第一端连接,所述第二上拉控制晶体管的栅极与所述第n-4级时脉信号连接,所述第二上拉控制晶体管的第二端与所述第n级栅极信号点以及所述下拉维持模块连接。

[0007]

于本揭示其中的一实施例中,所述级传模块包括第一级传模块晶体管及第二级传模块晶体管,所述第一级传模块晶体管的栅极和所述第二级传模块晶体管的栅极与所述第n级栅极信号点连接,所述第一级传模块晶体管的第一端和所述第二级传模块晶体管的第

一端分别与所述第一时脉信号和所述上拉模块连接,所述第一级传模块晶体管的第二端与所述第一输出信号连接,所述第二级传模块晶体管的第二端与第二输出信号连接。

[0008]

于本揭示其中的一实施例中,所述阵列基板行驱动电路还包括自举电容,所述上拉模块包括第一上拉晶体管,所述第一上拉晶体管的第一端与所述级传模块连接,所述第一上拉晶体管的第二端与所述自举电容连接。

[0009]

于本揭示其中的一实施例中,所述下拉维持模块包括第一下拉维持晶体管,第二下拉维持晶体管,第三下拉维持晶体管,第四下拉维持晶体管以及第五下拉维持晶体管,其中所述第一下拉维持晶体管的栅极、所述第二下拉维持晶体管的栅极、所述第三下拉晶体管的栅极、所述第四下拉晶体管的栅极及所述第五下拉维持晶体管的栅极与所述第n级反相栅极信号点连接,所述第一下拉维持晶体管的第一端与所述第n级水平扫描信号连接,所述第一下拉维持晶体管的第二端与所述第二恒压低电位连接,所述第二下拉维持晶体管的第一端与第一输出信号连接,所述第二下拉维持晶体管的第二端与所述第一恒压低电位连接,所述第三下拉维持晶体管的第一端与所述第二输出信号连接,所述第三下拉维持晶体管的第二端与所述下拉模块连接,所述第四下拉维持晶体管的第一端与所述第n级栅极信号点连接,所述第四下拉维持晶体管的第二端与第五下拉维持晶体管的第一端连接,所述第五下拉维持晶体管的第二端与所述第一恒压高电位连接。

[0010]

于本揭示其中的一实施例中,所述第二下拉维持晶体管的第二端还与所述第三下拉维持晶体管的第二端连接。

[0011]

于本揭示其中的一实施例中,所述结构反馈信号专职模块包括反馈晶体管,所述反馈晶体管的第一端与所述上拉控制模块连接,所述反馈晶体管的栅极与所述第一输出信号连接,所述反馈晶体管的第二端与所述第二输出信号连接。

[0012]

于本揭示其中的一实施例中,所述下拉维持栅极控制模块由下拉维持栅极晶体管构成,所述下拉维持栅极晶体管的第一端配置成接收第n级栅极反相信号,所述下拉维持栅极晶体管的栅极配置成接收第n-4级输出信号,所述下拉维持栅极晶体管根据所述第n级栅极反相信号与所述第n-4级输出信号开启或关闭。

[0013]

于本揭示其中的一实施例中,所述下拉维持栅极控制模块由下拉维持栅极晶体管构成,所述下拉维持栅极晶体管的第一端配置成接收第n级栅极反相信号,所述下拉维持栅极晶体管的栅极配置成接收根据所述第n-4级输出信号转换的第二第n-4级输出信号,所述下拉维持栅极晶体管根据所述第n级栅极反相信号与所述第二第n-4级输出信号开启或关闭。

[0014]

为达成上述目的,本揭示还提供一种显示装置,包括如上所述的阵列基板行驱动电路。

附图说明

[0015]

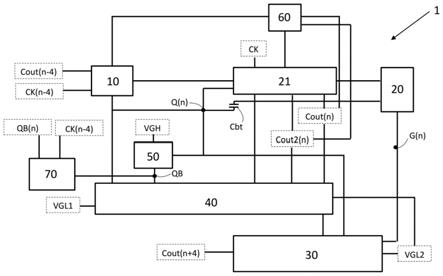

图1显示本揭示一实施例的阵列行驱动电路示意图;

[0016]

图2显示本揭示一实施例的阵列行驱动电路示意图;

[0017]

图3显示本揭示一实施例的阵列行驱动电路示意图;

[0018]

图4显示本揭示一实施例的显示装置示意图。

具体实施方式

[0019]

以下实施例的说明是参考附加的图示,用以例示本揭示可用以实施的特定实施例。本揭示所提到的方向用语,例如[上]、[下]、[前]、[后]、[左]、[右]、[内]、[外]、[侧面]等,仅是参考附加图式的方向。因此,使用的方向用语是用以说明及理解本揭示,而非用以限制本揭示。

[0020]

在图中,结构相似的单元是以相同标号表示。

[0021]

为解决上述问题,本揭示提出一种阵列基板行驱动电路及其显示装置,从而改善由于与第n级栅极信号点连接的晶体管在预充电阶段关闭不够彻底,而导致阵列基板行驱动电路在预充电阶段漏电的问题。

[0022]

请参阅图1,图1显示本揭示一实施例的阵列行驱动电路示意图。其中,阵列基板行驱动电路1,包括:上拉控制模块10,上拉控制模块10配置为接收第n-4级输出信号cout(n-4)及第n-4级时脉信号ck(n-4),上拉控制模块10与第n级栅极信号点q连接,第n级栅极信号点q输出第n级栅极信号q(n);级传模块21,级传模块21配置为接收第一时脉信号ck,与第一输出信号cout(n)及第二输出信号cout2(n)连接;上拉模块20,与级传模块21及第n级水平扫描信号g(n)连接;结构反馈信号模块60,配置为分别与第一输出信号cout(n)、第二输出信号cout2(n)及上拉控制模块10连接;下拉模块30,与第二恒压低电位vgl2、第n级水平扫描信号g(n)及第n+4级输出信号cout(n+4)连接;下拉维持模块40,与上拉控制模块10、下拉模块30、第一恒压低电位vgl1、第二恒压低电位vgl2以及第n级栅极信号点q连接;反相器50,与恒压高电位vgh、下拉维持模块40、第n级栅极信号点q及下拉模块30连接,反相器50在第n级反相栅极信号点qb输出第n级反相栅极信号qb(n);以及下拉维持栅极控制模块70,电连接在下拉维持模块40与反相器50之间,下拉维持栅极控制模块70根据第n级栅极反相信号qb(n)及第n-4级输出信号ck(n-4)开启或关闭。

[0023]

请参阅图2,图2显示本揭示一实施例的阵列行驱动电路示意图。其中,上拉控制模块10包括第一上拉控制晶体管t11及第二上拉控制晶体管t12,第一上拉控制晶体管t11的第一端配置为接收第n-4级输出信号cout(n-4),第一上拉控制晶体管t11的栅极配置为与第n-4级时脉信号ck(n-4)连接,第一上拉控制晶体管t11的第二端与第二上拉控制晶体管t12的第一端连接,第二上拉控制晶体管t12的栅极与第n-4级时脉信号ck(n-4)连接,第二上拉控制晶体管t12的第二端与第n级栅极信号点q以及下拉维持模块40连接。

[0024]

于本揭示其中的一实施例中,级传模块21包括第一级传模块晶体管t22及第二级传模块晶体管t23,第一级传模块晶体管t22的栅极和第二级传模块晶体管t23的栅极分别与第n级栅极信号点q连接,第一级传模块晶体管t22的第一端和第二级传模块晶体管t23的第一端分别与第一时脉信号ck和上拉模块10连接,第一级传模块晶体管t22的第二端与第一输出信号cout(n)连接,第二级传模块晶体管t23的第二端与第二输出信号cout2(n)连接。

[0025]

于本揭示其中的一实施例中,阵列基板行驱动电路1还包括自举电容cbt,上拉模块20包括第一上拉晶体管t21,第一上拉晶体管t21的第一端与级传模块21连接,第一上拉晶体管t21的第二端与自举电容cbt连接。

[0026]

于本揭示其中的一实施例中,下拉维持模块40包括第一下拉维持晶体管t41,第二下拉维持晶体管t42,第三下拉维持晶体管t43,第四下拉维持晶体管t44以及第五下拉维持

晶体管t45,其中第一下拉维持晶体管t41的栅极、第二下拉维持晶体管t42的栅极、第三下拉维持晶体管t43的栅极、第四下拉维持晶体管t44的栅极及第五下拉维持晶体管t45的栅极与第n级反相栅极信号qb(n)连接,第一下拉维持晶体管t41的第一端与第n级水平扫描信号g(n)连接,第一下拉维持晶体管t41的第二端与第二恒压低电位vgl2连接,第二下拉维持晶体管t42的第一端与第一输出信号cout(n)连接,第二下拉维持晶体管t42的第二端与第一恒压低电位vgl1连接,第三下拉维持晶体管t43的第一端与第二输出信号cout2(n)连接,第三下拉维持晶体管t43的第二端与下拉模块30连接,第四下拉维持晶体管t44的第一端与第n级栅极信号点q连接,第四下拉维持晶体管t44的第二端与第五下拉维持晶体管t45的第一端连接,第五下拉维持晶体管t45的第二端与第一恒压高电位vgl1连接。其中,第一传递晶体管t31的栅极连接第n+4级输出信号cout(n+4),第一传递晶体管t31的第一端连接第n级水平扫描信号g(n),第一传递晶体管t31的第二端连接第二恒压低电位vgl2,第二传递晶体管t32的第一端与第n级栅极信号点q、第二反相晶体管t52的栅极、第四反相晶体管t54的栅极连接,第二传递晶体管t32的栅极连接第n+4级输出信号cout(n+4),第二传递晶体管的第二端连接第三传递晶体管t33的第一端与第n级级联信号n(n),第三传递晶体管t33的栅极连接第n+4级输出信号cout(n+4),第三传递晶体管t33的第二端连接第一恒压低电位vgl1。

[0027]

请参阅图3,图3显示本揭示一实施例的阵列行驱动电路示意图。如图所示,于本揭示其中的一实施例中,第二下拉维持晶体管t42的第二端还与第三下拉维持晶体管t43的第二端连接。

[0028]

于本揭示其中的一实施例中,反相器50包括第一反相晶体管t51、第二反相晶体管t52、第三反相晶体管t53及第四反相晶体管t54,第一反相晶体管t51的第一端连接恒压高电位vgh,第一反相晶体管t51的栅极连接恒压高电位vgh,第一反相晶体管t51的第二端连接第二反相晶体管t52的第一端,第二反相晶体管t52的栅极连接第n级栅极信号点q,第二反相晶体管t52的第二端连接第一恒压低电位vgl1,第三反相晶体管t53的第一端连接第一反相晶体管t51的第一端,第三反相晶体管t53的栅极连接在第一反相晶体管t51的第二端与第二反相晶体管t52的第一端之间,第三反相晶体管t53的第二端连接第n级反相栅极信号点qb及第四反相晶体管t54的第一端,第四反相晶体管t54的栅极连接第n级栅极信号点q,第四反相晶体管t54的第二端连接第一恒压低电位vgl1。

[0029]

于本揭示其中的一实施例中,结构反馈信号专职模块60包括反馈晶体管t6,反馈晶体管t6的第一端与上拉控制模块10g以及第n级级联信号n(n)连接,反馈晶体管t6的栅极配置成与第一输出信号cout(n)连接,反馈晶体管t6的第二端与第二输出信号cout2(n)连接。

[0030]

于本揭示其中的一实施例中,下拉维持栅极控制模块70由下拉维持栅极晶体管t7构成,下拉维持栅极晶体管t7的第一端配置成接收第n级栅极反相信号qb(n),下拉维持栅极晶体管t7的栅极配置成接收第n-4级输出信号cout(n-4),下拉维持栅极晶体管t7根据第n级栅极反相信号qb(n)与所述第n-4级输出信号cout(n-4)开启或关闭,从而使下拉维持模块40中第四下拉维持晶体管t44与第五下拉维持晶体管t45更好的关闭,防止q(n)在预充电开始时与第四下拉维持晶体管t44及第五下拉维持晶体管t45形成漏电通道,达到提高第n级栅极信号点q的有效充电率的效果。

[0031]

于本揭示其中的一实施例中,下拉维持栅极控制模块70由下拉维持栅极晶体管t7构成,下拉维持栅极晶体管t7的第一端配置成接收第n级栅极反相信号,下拉维持栅极晶体管t7的栅极接收根据所述第n-4级输出信号cout(n-4)转换的第二第n-4级输出信号cout2(n-4),下拉维持栅极晶体管t7根据第n级栅极反相信号qb(n)与第二第n-4级输出信号cout2(n-4)开启或关闭,从而使下拉维持模块40中第四下拉维持晶体管t44与第五下拉维持晶体管t45更好的关闭,防止q(n)在预充电开始时与第四下拉维持晶体管t44及第五下拉维持晶体管t45形成漏电通道,达到提高第n级栅极信号点q的有效充电率的效果。

[0032]

其中,于本揭示的一实施例中,第二第n-4级输出信号cout2(n-4)可通过对外接的结构反馈信号模块输入第n-4级输出信号cout(n-4)转换产生,当下拉维持栅极晶体管t7以第二第n-4级输出信号cout2(n-4)作为栅极控制信号时,第三下拉维持晶体管t43的第二端还与第一恒压低电位vgl1连接。

[0033]

以下请进一步参照表1,其为本实施例提供的阵列基板行驱动电路与传统设计电路的q(n)及qb(n)下降时间的数值比较。

[0034][0035][0036]

表1

[0037]

如表1所示,当本实施例的goa电路设计与传统电路的q点预充电电压(q_precharge)与q点充电峰值电压(q_max)数值相当时,通过本设计提供的阵列基板行驱动电路进一步优化了q点预充电的效率,达到降低q点预充电时间的效果。

[0038]

请参阅图4,图4显示本揭示一实施例的显示装置示意图。本揭示还提供一种显示装置2,包括如上所述的阵列基板行驱动电路1。

[0039]

以上仅是本揭示的优选实施方式,应当指出,对于本领域普通技术人员,在不脱离本揭示原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本揭示的保护范围。

起点商标作为专业知识产权交易平台,可以帮助大家解决很多问题,如果大家想要了解更多知产交易信息请点击 【在线咨询】或添加微信 【19522093243】 与客服一对一沟通,为大家解决相关问题。

与客服一对一沟通,为大家解决相关问题。

此文章来源于网络,如有侵权,请联系删除

热门咨询

热门咨询

tips

商标分类

商标分类  商标转让

商标转让