驱动装置的输出电路的制作方法

2021-01-25 12:01:22|

2021-01-25 12:01:22| 293|

293| 起点商标网

起点商标网

[0001]

本发明涉及一种驱动装置的输出电路,尤其涉及一种可用于显示屏的源极驱动装置的输出电路。

背景技术:

[0002]

液晶显示器(liquid crystal display,lcd)具有外观轻薄、低功耗和低辐射等优点,已广泛应用于计算机屏幕、移动电话、个人数字助理(personal digital assistant,pda)、平板电视及其它通信/娱乐设备等各式各样的电子产品中。液晶显示器的原理是通过改变液晶层两端之间的电压差来改变液晶层中液晶分子的旋转角度,液晶层的透光度即可相应地改变,其进一步与背光模块提供的光源结合以显示图像。

[0003]

液晶显示器包括一驱动芯片,其中,一源极驱动装置被布置用来驱动液晶显示器上的数据线以改变其电压电平,从而控制液晶层中的液晶分子以在液晶显示屏上显示预期的图像。在液晶显示系统中,大多数功耗来自数据线的充电,且用来驱动数据线的源极驱动装置中的输出缓冲器具有大量的静态耗电。由于现代电子产品的低功耗需求,各厂商已开发了多种技术来减少驱动芯片(特别是源极驱动装置)的功耗。然而,现有的降功耗技术通常伴随着图像质量及/或显示效率的下降。因此,实有必要提供一种新颖的源极驱动装置结构,以在维持液晶显示器的显示性能的同时改善耗电效率。

技术实现要素:

[0004]

因此,本发明的主要目的即在于提供一种源极驱动装置的输出电路,其可在不降低显示屏显示性能的同时改善源极驱动装置的耗电。

[0005]

本发明的一实施例公开了一种驱动装置的输出电路,该输出电路包括多个输出节点、一第一输出缓冲器组及一多路复用器。该第一输出缓冲器组用来输出数据至该多个输出节点,其中,该第一输出缓冲器组中的每一输出缓冲器用来输出数据至该多个输出节点中的至少两个输出节点。该多路复用器耦接于该多个输出节点及该第一输出缓冲器组之间,用来选择将该第一输出缓冲器组中的每一输出缓冲器耦接至该多个输出节点的其中一输出节点。

[0006]

本发明的另一实施例公开了一种驱动装置的输出电路,该输出电路包括多个输出节点、一第一输出缓冲器及一多路复用器。该第一输出缓冲器用来输出数据至该多个输出节点。该多路复用器耦接于该多个输出节点及该第一输出缓冲器之间,用来选择将该第一输出缓冲器耦接至该多个输出节点的其中一输出节点。

附图说明

[0007]

图1为一般显示系统的示意图。

[0008]

图2示出了图1中的显示系统的详细结构。

[0009]

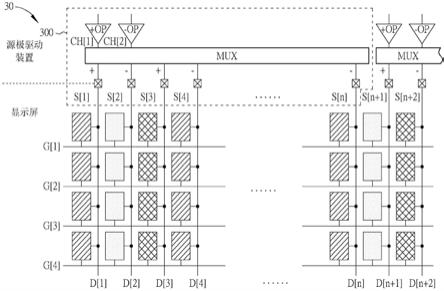

图3为本发明实施例一显示系统的示意图。

[0010]

图4示出了输出电路及其多路复用器的详细结构。

[0011]

图5为图3中的显示系统的波形图。

[0012]

图6a~6c为具有两个运算放大器而被布置用来通过四个输出节点驱动四条数据线的一输出缓冲器组的示意图。

[0013]

图7a~7d为多路复用器的操作及其相关数据流的示意图。

[0014]

图8为本发明实施例另一输出电路的示意图。

[0015]

图9及10为本发明实施例具有不同多路复用器结构的输出电路的示意图。

[0016]

图11为本发明实施例一源极驱动装置的示意图。

[0017]

图12a及12b为正常模式之下源极驱动装置中多路复用器的操作及其相关数据流的示意图。

[0018]

图13a~13f为省电模式之下源极驱动装置中多路复用器的操作及其相关数据流的示意图。

[0019]

图14为判断源极驱动装置的操作模式的示意图。

[0020]

图15为本发明实施例另一源极驱动装置的示意图。

[0021]

图16a~16d为图15中的源极驱动装置的详细操作方式及其相关数据流的示意图。

[0022]

其中,附图标记说明如下:

[0023]

10、30

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

显示系统

[0024]

102

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

显示屏

[0025]

104_1~104_4、1100、1500

ꢀꢀꢀꢀꢀꢀꢀꢀ

源极驱动装置

[0026]

106

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极驱动装置

[0027]

g[1]~g[4]

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极线

[0028]

d[1]~d[n]

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数据线

[0029]

s[1]~s[n]

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输出节点

[0030]

ch[1]、ch[2]

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

信道

[0031]

+op、-op

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

运算放大器

[0032]

300

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输出电路

[0033]

ld

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制信号

[0034]

ps_1~ps_4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

极性交换开关器

[0035]

ss_1~ss_n

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

选择开关器

[0036]

1110、1120、1510

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输出缓冲器组

[0037]

1130、1530

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

多路复用器

[0038]

l1_1~l1_n

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一数据锁存器

[0039]

l2_1~l2_n

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二数据锁存器

[0040]

+ls、-ls

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电平移位器

[0041]

+dac、-dac

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数字模拟转换器

具体实施方式

[0042]

请参考图1,图1为一般显示系统10的示意图。显示系统10包括一显示屏102、至少一源极驱动装置104_1~104_4及一栅极驱动装置106。显示屏102包括一子像素阵列,其中

每一子像素可根据来自于栅极驱动装置106的控制信号,从相应的源极驱动装置接收电压数据。一般来说,显示系统10可包括任意数量的源极驱动装置,视显示屏大小和分辨率而定,图1所示的四个源极驱动装置104_1~104_4仅作为一种范例。在一实施例中,栅极驱动装置106可设置于显示屏102的玻璃基板上,以实现阵列栅极驱动(gate-on-array,goa)结构。

[0043]

图2示出了显示系统10的详细结构。其中,每一子像素分别通过栅极线g[1]、g[2]、

…

连接至栅极驱动装置106,并分别通过数据线d[1]、d[2]、

…

、d[n]连接至一源极驱动装置。每一条数据线d[1]~d[n]都分别连接于一输出信道中的运算放大器(operational amplifier,op)并由运算放大器进行驱动。换句话说,每一运算放大器被布置用来通过相应的数据线驱动一列子像素。一般来说,运算放大器都具有基础静态耗电,若显示屏102具有高分辨率的需求而需要提高子像素的数量时,需使用更多运算放大器来支持更多的子像素列,在此情形下,静态耗电将成为显示系统10中需考虑的重要问题。

[0044]

为了降低整体耗电,应减少源极驱动装置中运算放大器的数量。因此,本发明提供了一种源极驱动装置,其中一运算放大器可用来驱动至少两条输出信道,或者一组运算放大器可用来驱动多于其运算放大器数量的输出信道。如此一来,可减少显示系统中的运算放大器数量,从而降低显示系统的电路成本和静态耗电。

[0045]

请参考图3,图3为本发明实施例一显示系统30的示意图。如图3所示,显示系统30包括一显示屏、一源极驱动装置及一栅极驱动装置(未示出)。为求简化,图3仅示出显示屏的一部分及其相应的源极驱动装置的输出电路300。输出电路300包括输出节点s[1]~s[n]、一输出缓冲器组及一多路复用器。输出节点s[1]~s[n]代表源极驱动装置上连接至显示屏的节点或端点,其可以是用来实现源极驱动装置的芯片或集成电路的输出导脚。输出缓冲器组包括数个输出缓冲器,而运算放大器可作为输出缓冲器,用来输出图像数据至输出节点s[1]~s[n]及显示屏。在此例中,输出缓冲器组包括具有正极性的运算放大器(+op)以及具有负极性的运算放大器(-op),分别用来输出正极性及负极性的图像数据。多路复用器耦接于输出节点s[1]~s[n]及输出缓冲器组之间,多路复用器可选择将输出缓冲器组中的各运算放大器耦接至输出节点s[1]~s[n]的其中一者,使得运算放大器可输出图像数据到相应的数据线。通过多路复用器的分时控制,每一运算放大器都可通过相应的输出节点输出图像数据到不同数据线。

[0046]

图4示出了输出电路300及其多路复用器的详细结构。为使两个运算放大器可输出图像数据至n个输出节点s[1]~s[n](其中n大于2),多路复用器可包括多个开关器,这些开关器可进行设定以控制各运算放大器在一数据周期内耦接至一输出节点,而不同的设定方式使得每一运算放大器可在不同数据周期内耦接至不同输出节点。

[0047]

请参考图5,图5为显示系统30的波形图。图5示出了信道ch[1]及ch[2](其分别对应于输出缓冲器组中的+op及-op)、输出节点s[1]~s[n]和栅极线g[1]~g[4]的波形以及相关控制信号ld和多路复用器(mux)设定。每一栅极线g[1]~g[4]可依序开启,以从时序控制器接收控制信号ld。在第一个数据周期中,多路复用器的设定可控制运算放大器连接至输出节点s[1]及s[2],使得信道ch[1]及ch[2]上的图像数据可分别通过多路复用器及输出节点s[1]及s[2]传送至子像素1_1及1_2。在下一个数据周期中,多路复用器的设定可控制运算放大器连接至输出节点s[3]及s[4],使得信道ch[1]及ch[2]上的图像数据可分别通过

多路复用器及输出节点s[3]及s[4]传送至子像素1_3及1_4。依此类推,在栅极线g[1]的最后一个数据周期中,多路复用器的设定可控制运算放大器连接至输出节点s[n-1]及s[n],使得信道ch[1]及ch[2]上的图像数据可分别通过多路复用器及输出节点s[n-1]及s[n]传送至子像素1_(n-1)及1_n。如此一来,第一行的每一子像素可从两个运算放大器接收图像数据。当第一行子像素接收到相应的图像数据之后,第一栅极线g[1]即可关闭。接着,栅极线g[2]、g[3]及g[4]依序开启,同时多路复用器及运算放大器执行相似的运作,以输出图像数据至第2、3、4行的子像素。

[0048]

在显示系统10中,每一列子像素都由各自的运算放大器进行驱动。相较之下,显示系统30具有多路复用器,使得一运算放大器可用来驱动多列子像素,因此,显示系统30中的整体运算放大器数量可大幅减少,从而降低运算放大器的整体静态耗电。

[0049]

为求简化,以下实施例叙述具有两个运算放大器的一输出缓冲器组通过四个输出节点来驱动四条数据线的情况,如图6a、6b及6c所示。图6a示出了源极驱动装置的输出电路结构,其中,具有两个运算放大器的输出缓冲器组可连接至四个输出节点并驱动四列子像素;图6b示出了输出电路及其多路复用器的详细结构;图6c示出了相关波形图。如图6a所示,每四列子像素可共享两个运算放大器(包括具有正极性的一运算放大器以及具有负极性的一运算放大器),使得源极驱动装置中的运算放大器数量减半(相较于图1所示的一般源极驱动装置10而言)。如图6b所示,这两个运算放大器(即输出缓冲器组)包括用来输出正极性图像数据的运算放大器(+op)以及用来输出负极性图像数据的运算放大器(-op)。当进行极性转换功能时,多路复用器的设置使得运算放大器可选择用来驱动耦接于输出节点s[1]及s[2]的数据线和子像素或驱动耦接于输出节点s[3]及s[4]的数据线和子像素。

[0050]

详细来说,多路复用器可包括多个开关器,分别耦接于输出缓冲器组和输出节点s[1]~s[4]其中一者之间。这些开关器可分类为极性交换开关器ps_1~ps_4和选择开关器ss_1~ss_8,如图6b所示。选择开关器ss_1~ss_8可用来控制输出缓冲器组中的运算放大器耦接至输出节点s[1]、s[2]或s[3]、s[4],而极性交换开关器ps_1~ps_4可用来控制每一数据线上的图像数据极性。

[0051]

输出电路可交替操作在一极性非交换模式及一极性交换模式之下。举例来说,在帧反转机制之下,关于极性的操作模式可在帧与帧之间切换;而在行反转机制之下,关于极性的操作模式可在行与行之间切换。图7a示出了极性非交换模式的第一个数据周期中多路复用器的运作方式及其相关数据流。如图7a所示,在此数据周期中,开关器ps_1、ps_4、ss_1及ss_4开启,而其它开关器关闭,因此输出缓冲器组耦接至输出节点s[1]及s[2]。更明确来说,正极性的运算放大器耦接至输出节点s[1]而负极性的运算放大器耦接至输出节点s[2],因此,正极性的图像数据被传送至输出节点s[1]而负极性的图像数据被传送至输出节点s[2]。接着,多路复用器的设定可在下一个数据周期改变。图7b示出了极性非交换模式的下一个数据周期中多路复用器的运作方式及其相关数据流。如图7b所示,在此数据周期中,开关器ps_1、ps_4、ss_5及ss_8开启,而其它开关器关闭,因此输出缓冲器组耦接至输出节点s[3]及s[4]。更明确来说,正极性的运算放大器耦接至输出节点s[3]而负极性的运算放大器耦接至输出节点s[4],因此,正极性的图像数据被传送至输出节点s[3]而负极性的图像数据被传送至输出节点s[4]。

[0052]

关于极性的操作模式是由极性交换开关器ps_1~ps_4来进行控制。如上所述,当

源极驱动装置操作在极性非交换模式时,极性交换开关器ps_1及ps_4开启。当源极驱动装置操作在极性交换模式时,可关闭极性交换开关器ps_1及ps_4并开启极性交换开关器ps_2及ps_3,以实现极性反转。图7c示出了极性交换模式的第一个数据周期中多路复用器的运作方式及其相关数据流。如图7c所示,在此数据周期中,开关器ps_2、ps_3、ss_2及ss_3开启,而其它开关器关闭,因此输出缓冲器组耦接至输出节点s[1]及s[2]。更明确来说,正极性的运算放大器耦接至输出节点s[2]而负极性的运算放大器耦接至输出节点s[1],因此,正极性的图像数据被传送至输出节点s[2]而负极性的图像数据被传送至输出节点s[1]。接着,多路复用器的设定可在下一个数据周期改变。图7d示出了极性交换模式的下一个数据周期中多路复用器的运作方式及其相关数据流。如图7d所示,在此数据周期中,开关器ps_2、ps_3、ss_6及ss_7开启,而其它开关器关闭,因此输出缓冲器组耦接至输出节点s[3]及s[4]。更明确来说,正极性的运算放大器耦接至输出节点s[4]而负极性的运算放大器耦接至输出节点s[3],因此,正极性的图像数据被传送至输出节点s[4]而负极性的图像数据被传送至输出节点s[3]。

[0053]

在一实施例中,输出电路的实现也可以不考虑极性反转,也就是说,输出电路所输出的每一图像数据都具有相同极性。在此情况下,一输出缓冲器组可仅包括单一运算放大器,其可用来驱动多条数据线并输出相应图像数据至多个输出节点。请参考图8,图8为本发明实施例另一输出电路800的示意图。如图8所示,输出缓冲器组仅包括单一运算放大器作为输出缓冲器,而多路复用器包括选择开关器ss_1~ss_n,用来选择将运算放大器耦接至输出节点s[1]~s[n]的其中一者。关于输出电路300的详细运作及实现方式也可应用于输出电路800,除了输出电路800不进行极性转换操作因而不需要极性交换开关器ps_1~ps_4。

[0054]

值得注意的是,极性反转是液晶显示器(liquid crystal display,lcd)常用的驱动方法。极性反转机制使得液晶显示器的显示屏上每一子像素可交替通过正极性和负极性进行驱动,从而避免长时间的同极性驱动之后出现残影。因此,输出电路300中的一输出缓冲器组包括正极性的运算放大器(+op)以及负极性的运算放大器(-op),可用于液晶显示屏的源极驱动装置,以实现极性反转和输出信道选择。另一方面,其它类型的显示屏(如有机发光二极管(organic light-emitting diode,oled)显示屏)不需采用极性反转技术,因此,不具有极性反转功能的输出电路800即适用于此类型的显示屏。只要输出电路中的一输出缓冲器可用来驱动多条数据线,且/或一特定数量的输出缓冲器可输出图像数据到数量更多的输出节点时,其驱动方法都属于本发明的范畴。

[0055]

另外需注意的是,本发明的目的在于提供一种源极驱动装置的输出电路,其可使用较少的输出缓冲器来驱动显示屏上的数据线。本领域技术人员当可据此进行修饰或变化,而不限于此。举例来说,上述多路复用器的结构仅为本发明众多实施方式当中的一种,实际上,多路复用器可通过任意方式实现。

[0056]

请参考图9,图9为本发明实施例一输出电路900的示意图。输出电路900的结构类似于图4中输出电路300的结构,其差异仅在于输出电路900中的多路复用器包括数量更多的极性交换开关器。在输出电路900的多路复用器中,极性交换开关器的数量与选择开关器的数量相等,而极性交换开关器以一对一的方式连接于选择开关器,也就是说,每一极性交换开关器都对应至一选择开关器。若相应的选择开关器和极性交换开关器都开启时,每一

运算放大器都可连接至所选择的输出节点。

[0057]

由于每一极性交换开关器都以一对一的对应方式连接至一选择开关器,因此,每一极性交换开关器可和其相应的选择开关器互相整合,以在每一输出信道上形成单一开关器,如图10所示。对每一运算放大器而言,若相应的开关器开启时,可连接至所选择的输出节点。

[0058]

如上所述,每一输出缓冲器都可用来驱动显示屏上的多条数据线,使得数据线可使用数量较少的输出缓冲器来进行驱动,以减少源极驱动装置中输出缓冲器的数量,从而降低耗电。如图5及6c所示,每一栅极线的开启周期是由一输出缓冲器驱动多条数据线的多个数据周期进行共享。举例来说,若一输出缓冲器用来驱动两条数据线时,每一数据线使用的驱动时间等于一栅极线开启周期的一半。若一输出缓冲器用来驱动n条数据线时,每一数据线使用的驱动时间等于一栅极线开启周期的1/n,以上情况可能导致数据线充电时间不足。为解决此问题,可选择性地执行利用一输出缓冲器来驱动多条数据线的省电操作。

[0059]

请参考图11,图11为本发明实施例一源极驱动装置1100的示意图。源极驱动装置1100包括一输出电路,此输出电路包括一第一输出缓冲器组1110、一第二输出缓冲器组1120、一多路复用器1130、以及输出节点s[1]~s[n]。第一输出缓冲器组1110包括具有正极性的一运算放大器以及具有负极性的一运算放大器,其它运算放大器则位于第二输出缓冲器组1120。每一输出缓冲器(如每一运算放大器)都可通过一对一的对应方式驱动相应的数据线并输出图像数据到相应的输出节点,并且耦接于一输入信道以及从该输入信道接收图像数据。输入信道可包括一第一数据锁存器(l1_1~l1_n)、一第二数据锁存器(l2_1~l2_n)、一电平移位器(正极性的+ls或负极性的-ls)、以及一数字模拟转换器(正极性的+dac或负极性的-dac)。多路复用器1130包括多个开关器,使得每一输出节点s[1]~s[n]可从相应的输出缓冲器(或者第一输出缓冲器组1110中的输出缓冲器)接收图像数据。在各输入信道中,可在第二数据锁存器(l2_1~l2_n)和电平移位器(+ls、-ls)之间设置一开关器,因此,每一输出缓冲器可根据开关器的控制,从所选择的数据锁存器接收图像数据。

[0060]

详细来说,源极驱动装置1100可选择操作在省电模式或正常模式。在正常模式之下,第一输出缓冲器组1110及第二输出缓冲器组1120都输出图像数据至输出节点s[1]~s[n]。多路复用器1130可进行布置使得每一输出节点s[1]~s[n]从相应的信道及输出缓冲器接收图像数据。图12a及12b示出了正常模式之下源极驱动装置1100中多路复用器的操作及相关数据流,其中,源极驱动装置1100中的所有运算放大器都输出图像数据到相应的输出节点。图12a示出了极性非交换模式之下的数据流,而图12b示出了极性交换模式之下的数据流。需注意的是,两相邻输入信道的第二数据锁存器和第一数据锁存器之间也可包括相连路径(未示出),从而实现极性交换的操作。

[0061]

在省电模式之下,第一输出缓冲器组1110输出图像数据至输出节点s[1]~s[n],同时第二输出缓冲器组1120关闭。在此情况下,第一输出缓冲器组1110中的运算放大器可在不同数据周期中分别输出图像数据至输出节点s[1]及s[2]、输出节点s[3]及s[4]、

…

、以及输出节点s[n-1]及s[n]。在省电模式中关闭的第二输出缓冲器组1120可降低源极驱动装置1100的耗电。在一实施例中,当一运算放大器被关闭时,也可同时关闭相应信道上的电平移位器及数字模拟转换器。图13a~13f示出了省电模式之下源极驱动装置1100中多路复用器的操作及其相关数据流,其中,第一输出缓冲器组1110中的运算放大器被开启,第二输出

缓冲器组1120中的运算放大器被关闭。图13a~13c示出了不同数据周期中极性非交换模式之下的数据流,而图13d~13f示出了不同数据周期中极性交换模式之下的数据流。在此例中,多路复用器及输入信道中的开关器可良好控制以从输入信道选择正确的图像数据并加以输出。本领域技术人员应可依据图13a~13f的内容搭配前述段落的说明来了解这些实施例的详细运作方式。

[0062]

源极驱动装置1100的结构提供了正常模式及省电模式的操作,其可由时序控制器利用一控制信号进行控制,及/或根据图像型态来决定。在一实施例中,当源极驱动装置1100从时序控制器接收控制信号时,源极驱动装置1100可得知接下来的图像帧应操作在正常模式或省电模式,并对应控制多路复用器及其开关器的设定。

[0063]

在另一实施例中,源极驱动装置1100可根据接收到的图像数据来判断应操作在正常模式或省电模式(而不是通过接收时序控制器的控制信号)。举例来说,当两个欲输出至相同数据线的连续图像数据之间的差异大于一临界值时,源极驱动装置1100可操作在正常模式,其中每一输出缓冲器都开启。当两个欲输出至相同数据线的连续图像数据之间的差异小于临界值时,源极驱动装置1100可操作在省电模式,其中部分输出缓冲器关闭而部分输出缓冲器被布置用来驱动多条数据线。

[0064]

若同一数据线上的两个连续图像数据之间的差异较小时,所需要的充电能力和充电时间较低,在此情况下,在一栅极线的开启周期内,运算放大器具有足够的时间来对多于一条数据线进行充电,即,每一数据线的充电时间仅占据栅极线开启周期的一部分。因此,当数据线上的差异较小时,应采用省电模式较佳。另一方面,若同一数据线上的两个连续图像数据之间的差异较大时,所需要的充电能力和充电时间较高,在此情况下,源极驱动装置1100应操作在正常模式,使得运算放大器具有足够的充电时间来对数据线进行充电。

[0065]

由于一运算放大器在省电模式中可用来驱动多于两条数据线,因此可考虑并结合至少两条数据线上的图像数据差异的比较结果来决定是否应执行省电模式。请参考图14,图14为判断源极驱动装置的操作模式的示意图。详细来说,输出节点s[1]上的两个连续图像数据可相互比较,以判断这两个图像数据的差异是否大于一临界值。若其差异大于临界值,则进行正常模式;否则,将一信号传送至一“及”逻辑模块(and)。另外,输出节点s[3]上的两个连续图像数据可相互比较,以判断这两个图像数据的差异是否大于一临界值。若其差异大于临界值,则进行正常模式;否则,将一信号传送至“及”逻辑模块。若“及”逻辑模块收到两侧的信号代表图像数据的差异小于临界值,因此,“及”逻辑模块可输出一信号以指示源极驱动装置操作在省电模式。在此情况下,对应于输出节点s[1]的运算放大器可在不同数据周期内输出图像数据至输出节点s[1]以及输出图像数据至输出节点s[3],而对应于输出节点s[3]的运算放大器则关闭,以降低耗电。在一实施例中,每一输入信道可包括一额外的数据锁存器,用来在图像数据进行比较之前存储图像数据,以根据操作模式将图像数据传送至所选择的输出缓冲器。

[0066]

请参考图15,图15为本发明实施例另一源极驱动装置1500的示意图。如图15所示,源极驱动装置1500包括一输出电路,其包括一输出缓冲器组1510、一多路复用器1530、以及输出节点s[1]~s[4]。输出缓冲器组1510中的各运算放大器耦接于一输入信道,其具有数据锁存器、电平移位器及数字模拟转换器。输出缓冲器组1510包括两个运算放大器,即具有正极性的运算放大器(+op)和具有负极性的运算放大器(-op),用来输出图像数据至四个输

出节点s[1]~s[4]。在此例中,每一输出节点都具有一组相应的数据锁存器,因此每一运算放大器可选择耦接至两组数据锁存器的其中一者,欲输出至一输出节点的图像数据可由相应的一组数据锁存器接收。举例来说,运算放大器可从数据锁存器l1_1及l2_1接收一第一图像数据,并在一第一数据周期中输出第一图像数据至输出节点s[1],接着从数据锁存器l1_3及l2_3接收一第二图像数据,并在一第二数据周期中输出第二图像数据至输出节点s[3]。关于极性非交换模式和极性交换模式之下源极驱动装置1500的详细操作方式及相关数据流示于图16a~16d。本领域技术人员应可依据图16a~16d的内容搭配前述段落的说明来了解其相关运作方式。

[0067]

在一实施例中,第二数据锁存器l2_1及l2_3可整合为单一数据锁存器,且/或第二数据锁存器l2_2及l2_4可整合为单一数据锁存器。

[0068]

为达到省电目的,也可省略或关闭部分不需要的运算放大器或输出缓冲器,而输入信道可通过任一方式实现,如图15或图11所示。在源极驱动装置中,根据电路结构,图像数据可通过数据锁存器、输出缓冲器、多路复用器及输出节点,以适当的方式传送。只要一输出缓冲器可用来驱动多条数据线且/或包括特定数量输出缓冲器的输出缓冲器组可输出图像数据到数量更多的输出节点,相关驱动方法都属于本发明的范畴。

[0069]

值得注意的是,本发明的目的在于,在源极驱动装置的输出电路中减少输出缓冲器的数量,以降低源极驱动装置的静态耗电。当输出电路中输出缓冲器数量减少的情况下,每一输出缓冲器都需用来输出图像数据至多个输出节点并驱动多条数据线。因此,可将一多路复用器设置于输出节点及输出缓冲器之间。在控制良好的多路复用器之下,每一输出缓冲器可在每一数据周期内耦接至所选择的输出节点,通过多路复用器的不同设定,输出缓冲器在不同数据周期内可耦接至不同输出节点。优选地,输出节点可以是芯片的输出导脚,而多路复用器与输出缓冲器可实现在同一芯片中。在此情况下,多路复用器及输出缓冲器可操作在相同电压范围内。此实现方式不同于多路复用器实作在显示屏的玻璃基板上的另一种电路。若多路复用器实作在玻璃基板上,则多路复用器的开关器须受控于高电压信号,因此需要额外的电平移位器来产生所需的高电压信号。除此之外,玻璃基板上的电路特性较芯片的电路特性差,这是因为芯片中的走线往往具有较低的寄生电容/电阻,且芯片中(用来实现开关器的)电路组件的效率优于玻璃基板上电路组件的效率。举例来说,芯片中的开关器相较于玻璃基板上的开关器而言能够较快地开启或关闭。再者,相较于现有的显示系统结构,本发明的源极驱动装置的结构修改方式只需要在输出电路中加入一多路复用器即可,此新式的源极驱动装置可应用于任何类型的显示屏或通过任何工艺制造的显示屏,无须额外修改或调整显示屏的结构。

[0070]

综上所述,本发明提供了一种源极驱动装置的输出电路,可减少输出缓冲器的数量以降低源极驱动装置的静态耗电。包括多个开关器的多路复用器可设置于输出节点及输出缓冲器之间,使得一输出缓冲器能够输出图像数据至多个输出节点并且驱动多条数据线。在不考虑是否进行极性反转的情况下,若每一输出缓冲器都能够驱动显示屏上的n条数据线,输出电路中输出缓冲器的整体数量可减少n倍。如此一来,可减少电路面积,同时降低静态耗电。

[0071]

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修

改、等同替换、改进等,均应包含在本发明的保护范围之内。

起点商标作为专业知识产权交易平台,可以帮助大家解决很多问题,如果大家想要了解更多知产交易信息请点击 【在线咨询】或添加微信 【19522093243】 与客服一对一沟通,为大家解决相关问题。

与客服一对一沟通,为大家解决相关问题。

此文章来源于网络,如有侵权,请联系删除

热门咨询

热门咨询

tips

商标分类

商标分类  商标转让

商标转让