一种分布式智适应动力模块的制作方法

2021-03-09 20:03:12|

2021-03-09 20:03:12| 664|

664| 起点商标网

起点商标网

[0001]

本实用新型涉及一种通风系统,特别是涉及一种分布式智适应动力模块。

背景技术:

[0002]

近几年通风系统开发成果显著,现有的动力分布式通风系统,其控制过程如下:每个支路末端均有支路风机,将支路风机的控制信号(0-10v)传输到plc进行加权计算以得出主风机的运行电压信号值,从而实现主风机根据系统变化进行调速运行。专利申请号2019216413962,名称为“动力分布式自平衡通风系统”,公开了干路和若干支路,所述干路上安装有主风机,全部或者部分支路上安装有支路风机,所有支路并联后再与干路串联,支路的末端接入各自对应的房间,其特征在于:所述主风机采用自适应风机或配备压力传感器的直流无刷风机,支路风机采用自适应风机或配备风速传感器的直流无刷风机;当主风机采用直流无刷风机时,配备的压力传感器设置在干路上,并位于该直流无刷风机的出风侧;当支路风机采用直流无刷风机时,配备的风速传感器设置在对应的支路上,并位于对应的直流无刷风机的出风侧或进风侧;且所述主风机和支路风机,至少一个为自适应风机。

技术实现要素:

[0003]

本实用新型旨在至少解决现有技术中存在的技术问题,特别创新地提出了一种分布式智适应动力模块。

[0004]

为了实现本实用新型的上述目的,本实用新型提供了一种分布式智适应动力模块,包括机箱,在所述机箱内设置有腔体隔断,所述腔体隔断将机箱分割成风机腔和出风降噪腔,腔体隔断上开有过风孔,所述机箱上设置有与风机腔相通的进风口、与出风降噪腔相通的出风口,且所述过风孔与出风口错开设置;还包括在所述风机腔内安装有一台智适应风机,过风孔供从智适应风机出来的气流进入出风降噪腔。

[0005]

在本实用新型的一种优选实施方式中,所述智适应风机包括风机和与所述风机相连的控制器,所述控制器包括处理器u1及与所述处理器u1相连的风机转速采集模块;

[0006]

风机转速采集模块包括:处理器u1的风机转速数据输入端pc4(hs)/tim1_ch4分别与电阻r60的第一端和三极管q7的集电极相连,电阻r60的第二端与+5v电源相连,三极管q7的发射极分别与电源地和电阻r46的第一端相连,电阻r46的第二端和三极管q7的基极分别与电阻r5的第一端和风机接口p2的风机转速输出端speed相连,电阻r5的第二端分别与电容c38的第一端和风机接口p2的电源输出端+10v相连,电容c38的第二端与电源地相连。通过风机输出的转速与风机接口p2的风机转速输出端speed相连,实现风机转速采集模块采集风机输出的转速输入到处理器u1,其利用风机输出的+10v电压,为风机输出的转速提供上拉电压。

[0007]

在本实用新型的一种优选实施方式中,在控制器上还包括风机转速输入模块,风机转速输入模块包括:处理器u1的风机转速数据输出端pc2(hs)tim1_ch2与电阻r13的第一端相连,电阻r13的第二端分别与电阻r14的第一端和电容c14的第一端相连,电阻r14的第

二端分别与电容c15的第一端和放大器u3a的正相输入端相连,电容c14的第二端和电容c15的第二端分别与电源地相连;放大器u3a的反相输入端分别与电阻r9的第一端和电阻r10的第一端相连,电阻r9的第二端与电源地相连,电阻r10的第二端分别与放大器u3a的输出端和电阻r43的第一端相连,电阻r43的第二端分别与电容c31的第一端、二极管dz2的负极和风机接口p2的风机转速数据输入端pwm相连,电容c31的第二端与电源地相连,二极管dz2的正极与电源地相连;风机接口p2的接地端与电源地相连。通过风机接口p2的转速数据输入端pwm与风机转速数据输入相连,其处理器u1输出不同占空比的pwm通过电阻r13、电阻r14、电容c14和电容c15构成的滤波电路后输入放大器u3a,放大器u3a输出不同电压值输入到风机,风机根据接收到转速数据,智能调节风机的转速。

[0008]

在本实用新型的一种优选实施方式中,在控制器上还包括电源模块,电源模块包括:电源接口j1的电源负端与电源地相连,电源接口j1的电源正端分别与电容c34的第一端、电容c13的第一端和电压芯片u2的电源电压端in相连,电容c34的第二端和电容c13的第二端分别与电源地相连;电压芯片u2的开关输出端sw分别与电容c1的第一端、电感l1的第一端相连,电容c1的第二端与电阻r4的第一端相连,电阻r4的第二端与电压芯片u2的引导端bst相连,电感l1的第二端分别与电容c11的第一端、电容c12的第一端、指示灯led1的正极、电容c35的第一端和电阻r8的第一端相连,电容c11的第二端和电容c12的第二端分别与电源地相连,指示灯led1的负极与电阻r2的第一端相连,电阻r2的第二端与电源地相连,电阻r8的第二端分别与电阻r7的第一端和电阻r21的第一端相连,电阻r21的第二端与电源地相连,电容c35的第二端与电阻r23的第一端相连,电阻r23的第二端和电阻r7的第二端分别与电压芯片u2的反馈端fb相连;电压芯片u2的使能端en分别与电阻r3的第一端和电容c2的第一端相连,电容c2的第二端与电源地相连,电阻r3的第二端与电源接口j1的电源正端相连。通过电源接口j1与+12v电源电压相连,电源接口j1输出+12v电源电压,+12v电源电压经电压芯片u2后输出稳定的+5v电源。

[0009]

在本实用新型的一种优选实施方式中,在控制器上还包括按键测试输入模块,按键测试输入模块包括:按键k1的第一端与电源地相连,按键k1的第二端分别与电阻r33的第一端和电阻r34的第一端相连,电阻r33的第二端与+5v电源相连,电阻r34的第二端与处理器u1的按键数据输入端pd3(hs)/tim2_ch2[adc_etr]相连。对风机进行测试时,长按按键k1后,系统进入测试模式,通过短按按键k1对风机档位进行设置。实现对风机档位测试。

[0010]

在本实用新型的一种优选实施方式中,在控制器上还包括数据转换模块,数据转换模块包括:处理器u1的使能端pd7/tli[tim1_ch4]分别与电阻r30的第一端、数据转换芯片u7的驱动器输出使能端de和数据转换芯片u7的接收器输出使能端re相连,电阻r30的第二端与+5v电源相连;数据转换芯片u7的接收器输出端ro与处理器u1的数据输入端pd6/uart2_rx相连,数据转换芯片u7的驱动器输入端di与处理器u1的数据输出端pd5/uart2_tx相连;数据转换芯片u7的电源电压端vcc分别与+5v电源和电容c26的第一端相连,电容c26的第二端与电源地相连;数据转换芯片u7的电源地端gnd与电源地相连;数据转换芯片u7的数据端b与电阻r27的第一端相连,电阻r27的第二端分别与电阻r28的第一端、电阻r32的第一端、瞬态抑制二极管z2的第一端和熔断器f1的第一端相连,电阻r32的第二端与电源地相连,数据转换芯片u7的数据端a与电阻r29的第一端相连,电阻r29的第二端分别与电阻r28的第二端、电阻r31的第一端、瞬态抑制二极管z1的第一端和熔断器f2的第一端相连,电阻

r31的第二端与+5v电源相连,瞬态抑制二极管z1的第二端和瞬态抑制二极管z2的第二端分别与电源地相连,熔断器f1的第二端与数据接口p8的数据第一端相连,熔断器f2的第二端与数据接口p8的数据第二端相连。通过数据接口p8与数据通信端子连接,实现数据通讯。

[0011]

在本实用新型的一种优选实施方式中,在控制器上还包括风机驱动模块,风机驱动模块包括:处理器u1的驱动数据端[tim1_ch3n]ain2/pb2与驱动芯片u5的驱动输入端1b相连,处理器u1的驱动数据端[tim1_etr/ain3/pb3与驱动芯片u5的驱动输入端2b相连,处理器u1的驱动数据端[i2c_scl]ain4/pb4与驱动芯片u5的驱动输入端3b相连,处理器u1的驱动数据端[i2c_sda]ain5/pb5与驱动芯片u5的驱动输入端4b相连;

[0012]

驱动芯片u5的驱动输出端1c与风机驱动接口p5的驱动输入第一端相连,驱动芯片u5的驱动输出端2c与风机驱动接口p5的驱动输入第二端相连,驱动芯片u5的驱动输出端3c与风机驱动接口p5的驱动输入第三端相连,驱动芯片u5的驱动输出端4c与风机驱动接口p5的驱动输入第四端相连,风机驱动接口p5的电源端与+12v电源相连;

[0013]

驱动芯片u5的公共端com分别与+12v电源和电容c24的第一端相连,驱动芯片u5的公共地端e分别与电源地和电容c24的第二端相连。通过风机驱动接口p5与风机输入端相连,实现处理器u1通过风机驱动模块驱动风机工作。

[0014]

在本实用新型的一种优选实施方式中,在控制器上还包括风机转速档位设置模块,风机转速档位设置模块包括:处理器u1的数据输入端[tim1_ch1n]ain0/pb0分别与接口j2的输出第一端、接口j2的输出第二端、接口j2的输出第三端、接口j2的输出第四端、接口j2的输出第五端、接口j2的输出第六端、接口j2的输出第七端和接口j2的输出第八端相连;

[0015]

接口j2的输入第一端分别与电阻组rn10的第一电阻第一端和电阻组rn10的第二电阻第一端相连,接口j2的输入第二端分别与电阻组rn10的第三电阻第一端和电阻组rn10的第四电阻第一端相连,接口j2的输入第三端分别与电阻组rn9的第一电阻第一端和电阻组rn9的第二电阻第一端相连,接口j2的输入第四端分别与电阻组rn9的第三电阻第一端和电阻组rn9的第四电阻第一端相连;

[0016]

接口j2的输入第五端分别与电阻组rn9的第二电阻第二端和电阻组rn9的第三电阻第二端相连,接口j2的输入第六端分别与电阻组rn9的第一电阻第二端和电阻组rn10的第四电阻第二端相连,接口j2的输入第七端分别与电阻组rn10的第二电阻第二端和电阻组rn10的第三电阻第二端相连,接口j2的输入第八端分别与电阻组rn10的第一电阻第二端和+5v电源相连,电阻组rn9的第四电阻第二端与电源地相连。通过跳线帽将接口j2的输出第一端和接口j2的输入第一端相连,或者通过跳线帽将接口j2的输出第二端和接口j2的输入第二端相连,或者通过跳线帽将接口j2的输出第三端和接口j2的输入第三端相连,或者通过跳线帽将接口j2的输出第四端和接口j2的输入第四端相连,或者通过跳线帽将接口j2的输出第五端和接口j2的输入第五端相连,或者通过跳线帽将接口j2的输出第六端和接口j2的输入第六端相连,或者通过跳线帽将接口j2的输出第七端和接口j2的输入第七端相连,或者通过跳线帽将接口j2的输出第八端和接口j2的输入第八端相连;实现输入不同的电压值,来对应设定其风机最大转速。

[0017]

在本实用新型的一种优选实施方式中,在控制器上还包括风机转速档位显示模块,风机转速档位显示模块包括:处理器u1的数据端pd4(hs)/tim2_ch1[beep]与电阻r25的第一端相连,电阻r25的第二端与显示驱动芯片u8的数据端din相连,显示驱动芯片u8的电

源端vdd分别与+5v电源和电容c27的第一端相连,显示驱动芯片u8的电源地端gnd分别与电源地和电容c27的第二端相连;

[0018]

显示驱动芯片u8的七段数据端a与七段数码管led2的七段数据端a相连,显示驱动芯片u8的七段数据端b与七段数码管led2的七段数据端b相连,显示驱动芯片u8的七段数据端c与七段数码管led2的七段数据端c相连,显示驱动芯片u8的七段数据端d与七段数码管led2的七段数据端d相连,显示驱动芯片u8的七段数据端e与七段数码管led2的七段数据端e相连,显示驱动芯片u8的七段数据端f与七段数码管led2的七段数据端f相连,显示驱动芯片u8的七段数据端g与七段数码管led2的七段数据端g相连,显示驱动芯片u8的数据点端h与七段数码管led2的数据点端dp相连,显示驱动芯片u8的公共端gr0与七段数码管led2的公共端com相连。风机测试时,处理器u1向风机转速档位显示模块输入风机转速,七段数码管led2上显示测试的风机转速档位,便于测试员测试。

[0019]

在本实用新型的一种优选实施方式中,在控制器上还包括显示屏数据采集模块,显示屏数据采集模块包括:处理器u1的显示屏数据采集端[tim1_ch2n]ain1/pb1分别与电阻r24的第一端、电阻r26的第一端和电容c23的第一端相连,电阻r24的第二端分别与电容c22的第一端和接口j8输出端相连,接口j8接地端与电源地相连,电容c22的第二端、电容c23的第二端和电阻r26的第二端分别与电源地相连。通过接口j8与显示屏数据输出端相连,显示屏数据输出端输出0v~10v的电平信号,实现对显示屏数据的采集。

[0020]

在本实用新型的一种优选实施方式中,在控制器上还包括风机脉冲数设置模块,风机脉冲数设置模块包括:处理器u1的数据端pg0分别与电阻组rn7的第一电阻第一端和开关组sw1的第一开关第一端相连,处理器u1的数据端pg1分别与电阻组rn7的第二电阻第一端和开关组sw1的第二开关第一端相连,处理器u1的数据端pe3/tim1_bkin分别与电阻组rn7的第三电阻第一端和开关组sw1的第三开关第一端相连,处理器u1的数据端pe0(hs)/clk_cco分别与电阻组rn7的第四电阻第一端和开关组sw1的第四开关第一端相连,处理器u1的数据端pe1(t)/i2c_scl分别与电阻组rn8的第三电阻第一端和开关组sw1的第五开关第一端相连,处理器u1的数据端pe2(t)i2c_sda分别与电阻组rn8的第四电阻第一端和开关组sw1的第六开关第一端相连;

[0021]

电阻组rn7的第一电阻第二端、电阻组rn7的第二电阻第二端、电阻组rn7的第三电阻第二端、电阻组rn7的第四电阻第二端、电阻组rn8的第三电阻第二端、电阻组rn8的第四电阻第二端分别与电源地相连;

[0022]

开关组sw1的第一开关第二端、开关组sw1的第二开关第二端、开关组sw1的第三开关第二端、开关组sw1的第四开关第二端、开关组sw1的第五开关第二端和开关组sw1的第六开关第二端分别与电源地相连。通过开关组sw1闭合和断开开关实现风机脉冲数的设置,其脉冲数个数为0~63个。

[0023]

综上所述,由于采用了上述技术方案,本实用新型能够通过智适应风机智能调节风机的转速。

[0024]

本实用新型的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本实用新型的实践了解到。

附图说明

[0025]

本实用新型的上述和/或附加的方面和优点从结合下面附图对实施例的描述中将变得明显和容易理解,其中:

[0026]

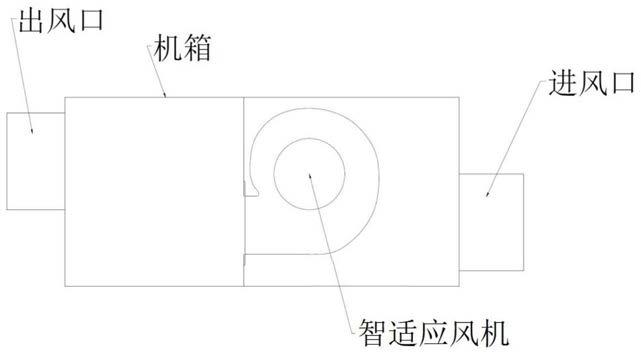

图1是本实用新型结构示意图。

[0027]

图2是本实用新型连接示意框图。

[0028]

图3是本实用新型处理器电路连接示意图。

[0029]

图4是本实用新型风机转速采集模块电路连接示意图。

[0030]

图5是本实用新型第二风机转速采集模块电路连接示意图。

[0031]

图6是本实用新型第三风机转速采集模块电路连接示意图。

[0032]

图7是本实用新型电源模块电路连接示意图。

[0033]

图8是本实用新型按键测试输入模块电路连接示意图。

[0034]

图9是本实用新型数据转换模块电路连接示意图。

[0035]

图10是本实用新型风机驱动模块电路连接示意图。

[0036]

图11是本实用新型风机转速档位设置模块电路连接示意图。

[0037]

图12是本实用新型第二风机转速档位设置模块电路连接示意图。

[0038]

图13是本实用新型第三风机转速档位设置模块电路连接示意图。

[0039]

图14是本实用新型风机转速档位显示模块电路连接示意图。

[0040]

图15是本实用新型显示屏数据采集模块电路连接示意图。

[0041]

图16是本实用新型风机脉冲数设置模块电路连接示意图。

[0042]

图17是本实用新型spi接口模块电路连接示意图。

具体实施方式

[0043]

下面详细描述本实用新型的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本实用新型,而不能理解为对本实用新型的限制。

[0044]

本实用新型提供了一种分布式智适应动力模块,如图1所示,包括机箱,在所述机箱内设置有腔体隔断,所述腔体隔断将机箱分割成风机腔和出风降噪腔,腔体隔断上开有过风孔,所述机箱上设置有与风机腔相通的进风口、与出风降噪腔相通的出风口,且所述过风孔与出风口错开设置;还包括在所述风机腔内安装有一台智适应风机,过风孔供从智适应风机出来的气流进入出风降噪腔。

[0045]

在本实用新型的一种优选实施方式中,所述智适应风机包括风机和与所述风机相连的控制器,其风机和控制器可以集成在一起,也可以是单独的模块。所述控制器包括处理器u1及与所述处理器u1相连的风机转速采集模块;该风机转速采集模块为第一风机转速采集模块;在本实施方式中,如图3所示,处理器u1的i/0电源地端vssio_1和处理器u1的数字电源地端vss分别与电容c3的第一端和电源地相连,电容c3的第二端与处理器u1的稳压器电容端vcap相连;处理器u1的数字电源端vdd和处理器u1的i/o电源端vddio_1分别与电容c4的第一端、电容c5的第一端、电容c6的第一端和+5v电源相连,电容c4的第二端、电容c5的第二端和电容c6的第二端分别与电源地相连;处理器u1的模拟电源端vdda分别与电容c8的

第一端、电容c9的第一端和+5v电源相连,处理器u1的模拟电源地端vssa分别与电容c8的第二端、电容c9的第二端和电源地相连;处理器u1的i/o电源端vddio_2分别与电容c10的第一端和+5v电源相连,处理器u1的i/o电源地端vssio_2分别与电容c10的第二端和电源地相连;处理器u1的重启端nrst分别与电容c7的第一端、电阻r1的第一端和重启接口p1的第三端相连,电容c7的第二端与电源地相连,电阻r1的第二端与+5v电源相连,重启接口p1的第二端与处理器u1的swim数据端pd1(hs)/swim相连,重启接口p1的第一端与+5v电源相连,重启接口p1的第四端与电源地相连;在本实施方式中,电容c3、电容c6、电容c7、电容c9、电容c10的容值为0.1uf,电容c4的容值为10uf,电容c5、电容c8的容值为1uf,电阻r1的阻值为10k,处理器u1的型号为stm8s005c6t6。

[0046]

第一风机转速采集模块包括:如图2~4所示,处理器u1的风机转速数据输入端pc4(hs)/tim1_ch4分别与电阻r60的第一端和三极管q7的集电极相连,电阻r60的第二端与+5v电源相连,三极管q7的发射极分别与电源地和电阻r46的第一端相连,电阻r46的第二端和三极管q7的基极分别与电阻r5的第一端和风机接口p2的风机转速输出端speed相连,电阻r5的第二端分别与电容c38的第一端和风机接口p2的电源输出端+10v相连,电容c38的第二端与电源地相连。在本实施方式中,电阻r60、电阻r46、电阻r5的阻值为10k,电容c38的容值为4.7uf,风机接口p2采用5.08螺钉式连接器,三极管q7为npn型三极管,具体为贴片y1。

[0047]

在本实用新型的一种优选实施方式中,在控制器上还包括风机转速输入模块,该风机转速输入模块为第一风机转速输入模块,第一转速输出模块包括:如图2~4所示,处理器u1的风机转速数据输出端pc2(hs)tim1_ch2与电阻r13的第一端相连,电阻r13的第二端分别与电阻r14的第一端和电容c14的第一端相连,电阻r14的第二端分别与电容c15的第一端和放大器u3a的正相输入端相连,电容c14的第二端和电容c15的第二端分别与电源地相连;放大器u3a的反相输入端分别与电阻r9的第一端和电阻r10的第一端相连,电阻r9的第二端与电源地相连,电阻r10的第二端分别与放大器u3a的输出端和电阻r43的第一端相连,电阻r43的第二端分别与电容c31的第一端、二极管dz2的负极和风机接口p2的风机转速数据输入端pwm相连,电容c31的第二端与电源地相连,二极管dz2的正极与电源地相连;风机接口p2的接地端与电源地相连。在本实施方式中,电阻r9、电阻r13、电阻r14的阻值为1k,电阻r10的阻值为3.3k,电阻r43的阻值为110ω,电容c14、电容c15、电容c31的容值为10uf,放大器u3a的型号为lm258drg4,二极管dz2采用12v稳压管。

[0048]

在本实用新型的一种优选实施方式中,在控制器上还包括第二风机转速采集模块,第二风机转速采集模块包括:如图2、3和5所示,处理器u1的风机转速数据输入端pe5/spi_nss分别与电阻r61的第一端和三极管q8的集电极相连,电阻r61的第二端与+5v电源相连,三极管q8的发射极分别与电源地和电阻r47的第一端相连,电阻r47的第二端和三极管q8的基极分别与电阻r22的第一端和风机接口p3的风机转速输出端speed相连,电阻r22的第二端分别与电容c39的第一端和风机接口p3的电源输出端+10v相连,电容c39的第二端与电源地相连。在本实施方式中,电阻r61、电阻r47、电阻r22的阻值为10k,电容c39的容值为4.7uf,风机接口p3采用5.08螺钉式连接器,三极管q8为npn型三极管,具体为贴片y1。

[0049]

在本实用新型的一种优选实施方式中,在控制器上还包括第二风机转速输入模块,第二风机转速输入模块包括:如图2、3和5所示,处理器u1的风机转速数据输出端pc1(hs)tim1_ch1/uart2_ck与电阻r19的第一端相连,电阻r19的第二端分别与电阻r20的第一

端和电容c20的第一端相连,电阻r20的第二端分别与电容c21的第一端和放大器u3b的正相输入端相连,电容c20的第二端和电容c21的第二端分别与电源地相连;放大器u3b的电源端分别与+12v电源和电容c18的第一端相连,电容c18的第二端与电源地相连,放大器u3b的电源地端与电源地相连,放大器u3b的反相输入端分别与电阻r17的第一端和电阻r18的第一端相连,电阻r17的第二端与电源地相连,电阻r18的第二端分别与放大器u3b的输出端和电阻r44的第一端相连,电阻r44的第二端分别与电容c32的第一端、二极管dz4的负极和风机接口p3的风机转速数据输入端pwm相连,电容c32的第二端与电源地相连,二极管dz4的正极与电源地相连;风机接口p3的接地端与电源地相连。在本实施方式中,电阻r17、电阻r19、电阻r20的阻值为1k,电阻r18的阻值为3.3k,电阻r44的阻值为110ω,电容c20、电容c21、电容c32的容值为10uf,电容c18的容值为0.1uf,二极管dz4采用12v稳压管,放大器u3b的型号为lm258drg4,放大器u3a和放大器u3b共用一个双运放放大器。

[0050]

在本实用新型的一种优选实施方式中,在控制器上还包括第三风机转速采集模块,第三风机转速采集模块包括:如图2、3和6所示,处理器u1的风机转速数据输入端pd2(hs)tim3_ch1[tim2_ch3]分别与电阻r62的第一端和三极管q9的集电极相连,电阻r62的第二端与+5v电源相连,三极管q9的发射极分别与电源地和电阻r45的第一端相连,电阻r45的第二端和三极管q9的基极分别与电阻r6的第一端和风机接口p4的风机转速输出端speed相连,电阻r6的第二端分别与电容c37的第一端和风机接口p4的电源输出端+10v相连,电容c37的第二端与电源地相连。在本实施方式中,电阻r62、电阻r45、电阻r6的阻值为10k,电容c37的容值为4.7uf,风机接口p4采用5.08螺钉式连接器,三极管q9为npn型三极管,具体为贴片y1。

[0051]

在本实用新型的一种优选实施方式中,在控制器上还包括第三风机转速输入模块,第三风机转速输入模块包括:如图2、3和6所示,处理器u1的风机转速数据输出端pc3(hs)tim1_ch3与电阻r15的第一端相连,电阻r15的第二端分别与电阻r16的第一端和电容c16的第一端相连,电阻r16的第二端分别与电容c17的第一端和放大器u3c的正相输入端相连,电容c16的第二端和电容c17的第二端分别与电源地相连;放大器u3c的电源端分别与电容c19的第一端和+12v电源相连,电容c19的第二端与电源地相连,放大器u3c的电源地端与电源地相连,放大器u3c的反相输入端分别与电阻r11的第一端和电阻r12的第一端相连,电阻r11的第二端与电源地相连,电阻r12的第二端分别与放大器u3c的输出端和电阻r42的第一端相连,电阻r42的第二端分别与电容c30的第一端、二极管dz3的负极和风机接口p4的风机转速数据输入端pwm相连,电容c30的第二端与电源地相连,二极管dz3的正极与电源地相连;风机接口p4的接地端与电源地相连。在本实施方式中,电阻r11、电阻r15、电阻r16的阻值为1k,电阻r12的阻值为3.3k,电阻r42的阻值为110ω,电容c16、电容c17、电容c30的容值为10uf,电容c19的容值为0.1uf,二极管dz3采用12v稳压管,放大器u3c的型号为lm258drg4。

[0052]

在本实用新型的一种优选实施方式中,在控制器上还包括电源模块,电源模块包括:如图2和7所示,电源接口j1的电源负端与电源地相连,电源接口j1的电源正端分别与电容c34的第一端、电容c13的第一端和电压芯片u2的电源电压端in相连,电容c34的第二端和电容c13的第二端分别与电源地相连;电压芯片u2的开关输出端sw分别与电容c1的第一端、电感l1的第一端相连,电容c1的第二端与电阻r4的第一端相连,电阻r4的第二端与电压芯

片u2的引导端bst相连,电感l1的第二端分别与电容c11的第一端、电容c12的第一端、指示灯led1的正极、电容c35的第一端和电阻r8的第一端相连,电容c11的第二端和电容c12的第二端分别与电源地相连,指示灯led1的负极与电阻r2的第一端相连,电阻r2的第二端与电源地相连,电阻r8的第二端分别与电阻r7的第一端和电阻r21的第一端相连,电阻r21的第二端与电源地相连,电容c35的第二端与电阻r23的第一端相连,电阻r23的第二端和电阻r7的第二端分别与电压芯片u2的反馈端fb相连;电压芯片u2的使能端en分别与电阻r3的第一端和电容c2的第一端相连,电容c2的第二端与电源地相连,电阻r3的第二端与电源接口j1的电源正端相连。在本实施方式中,电阻r2的阻值为680ω,电阻r4的阻值为10ω,电阻r3的阻值为100k,电阻r7的阻值为75k,电阻r8的阻值为40.2k,电阻r21的阻值为7.86k,电阻r23的阻值为10k,电容c12、电容c34的容值为22uf,电容c11、电容c13、电容c1、电容c2、电容c35的容值为0.1uf,电感l1的容值为6.8uh,电压芯片u2的型号为mp1470gj-z,电源接口j1采用5.08螺钉式连接器。

[0053]

在本实用新型的一种优选实施方式中,在控制器上还包括按键测试输入模块,该按键测试输入模块为按键测试第一风机输入模块,按键测试第一风机输入模块包括:如图2、3和8所示,按键k1的第一端与电源地相连,按键k1的第二端分别与电阻r33的第一端和电阻r34的第一端相连,电阻r33的第二端与+5v电源相连,电阻r34的第二端与处理器u1的按键数据输入端pd3(hs)/tim2_ch2[adc_etr]相连。在本实施方式中,电阻r33的阻值为100k,电阻r34的阻值为470ω。

[0054]

在控制器上还包括按键测试第二风机输入模块,按键测试第二风机输入模块包括:如图2、3和8所示,按键k2的第一端与电源地相连,按键k2的第二端分别与电阻r35的第一端和电阻r36的第一端相连,电阻r35的第二端与+5v电源相连,电阻r36的第二端与处理器u1的按键数据输入端pd0(hs)/tim3_ch2[tim1_bkin][clk_cco]相连。在本实施方式中,电阻r35的阻值为100k,电阻r36的阻值为470ω。

[0055]

在控制器上还包括按键测试第三风机输入模块,按键测试第三风机输入模块包括:如图2、3和8所示,按键k3的第一端与电源地相连,按键k3的第二端分别与电阻r37的第一端和电阻r38的第一端相连,电阻r37的第二端与+5v电源相连,电阻r38的第二端与处理器u1的按键数据输入端pc7(hs)/spi_miso相连。在本实施方式中,电阻r37的阻值为100k,电阻r38的阻值为470ω。

[0056]

在本实用新型的一种优选实施方式中,在控制器上还包括数据转换模块,数据转换模块包括:如图2、3和9所示,处理器u1的使能端pd7/tli[tim1_ch4]分别与电阻r30的第一端、数据转换芯片u7的驱动器输出使能端de和数据转换芯片u7的接收器输出使能端re相连,电阻r30的第二端与+5v电源相连;数据转换芯片u7的接收器输出端ro与处理器u1的数据输入端pd6/uart2_rx相连,数据转换芯片u7的驱动器输入端di与处理器u1的数据输出端pd5/uart2_tx相连;数据转换芯片u7的电源电压端vcc分别与+5v电源和电容c26的第一端相连,电容c26的第二端与电源地相连;数据转换芯片u7的电源地端gnd与电源地相连;数据转换芯片u7的数据端b与电阻r27的第一端相连,电阻r27的第二端分别与电阻r28的第一端、电阻r32的第一端、瞬态抑制二极管z2的第一端和熔断器f1的第一端相连,电阻r32的第二端与电源地相连,数据转换芯片u7的数据端a与电阻r29的第一端相连,电阻r29的第二端分别与电阻r28的第二端、电阻r31的第一端、瞬态抑制二极管z1的第一端和熔断器f2的第

一端相连,电阻r31的第二端与+5v电源相连,瞬态抑制二极管z1的第二端和瞬态抑制二极管z2的第二端分别与电源地相连,熔断器f1的第二端与数据接口p8的数据第一端相连,熔断器f2的第二端与数据接口p8的数据第二端相连。在本实施方式中,电阻r30的阻值为10k,电阻r27、电阻r29的阻值为100ω,电阻r28的阻值为120ω,电阻r31、电阻r32的阻值为10k,瞬态抑制二极管z1、瞬态抑制二极管z2的型号为p0080sa,熔断器f1、熔断器f2限流140ma,数据接口p8为485连接器,电容c26的容值为0.1uf,数据转换芯片u7的型号为ssp485。

[0057]

在本实用新型的一种优选实施方式中,在控制器上还包括风机驱动模块,该风机驱动模块为第一风机驱动模块,第一风机驱动模块包括:如图2、3和10所示,处理器u1的驱动数据端[tim1_ch3n]ain2/pb2与驱动芯片u5的驱动输入端1b相连,处理器u1的驱动数据端[tim1_etr/ain3/pb3与驱动芯片u5的驱动输入端2b相连,处理器u1的驱动数据端[i2c_scl]ain4/pb4与驱动芯片u5的驱动输入端3b相连,处理器u1的驱动数据端[i2c_sda]ain5/pb5与驱动芯片u5的驱动输入端4b相连;

[0058]

驱动芯片u5的驱动输出端1c与风机驱动接口p5的驱动输入第一端相连,驱动芯片u5的驱动输出端2c与风机驱动接口p5的驱动输入第二端相连,驱动芯片u5的驱动输出端3c与风机驱动接口p5的驱动输入第三端相连,驱动芯片u5的驱动输出端4c与风机驱动接口p5的驱动输入第四端相连,风机驱动接口p5的电源端与+12v电源相连;

[0059]

驱动芯片u5的公共端com分别与+12v电源和电容c24的第一端相连,驱动芯片u5的公共地端e分别与电源地和电容c24的第二端相连。在本实施方式中,驱动芯片u5采用uln200xx系列的芯片,电容c24的容值为0.1uf。

[0060]

在本实用新型的一种优选实施方式中,在控制器上还包括第二风机驱动模块,第二风机驱动模块包括:如图2、3和10所示,处理器u1的驱动数据端ain6/pb6与驱动芯片u5的驱动输入端5b相连,处理器u1的驱动数据端ain7/pb7与驱动芯片u5的驱动输入端6b相连,处理器u1的驱动数据端(hs)pa6与驱动芯片u6的驱动输入端2b相连,处理器u1的驱动数据端(hs)pa5与驱动芯片u6的驱动输入端3b相连;

[0061]

驱动芯片u5的驱动输出端5c与风机驱动接口p6的驱动输入第一端相连,驱动芯片u5的驱动输出端6c与风机驱动接口p6的驱动输入第二端相连,驱动芯片u6的驱动输出端2c与风机驱动接口p6的驱动输入第三端相连,驱动芯片u6的驱动输出端3c与风机驱动接口p6的驱动输入第四端相连,风机驱动接口p6的电源端与+12v电源相连;

[0062]

驱动芯片u6的公共端com分别与+12v电源和电容c25的第一端相连,驱动芯片u6的公共地端e分别与电源地和电容c25的第二端相连。在本实施方式中,驱动芯片u6采用uln200xx系列的芯片,电容c25的容值为0.1uf。

[0063]

在本实用新型的一种优选实施方式中,在控制器上还包括第三风机驱动模块,第三风机驱动模块包括:如图2、3和10所示,处理器u1的驱动数据端(hs)pa4与驱动芯片u6的驱动输入端4b相连,处理器u1的驱动数据端[tim3_ch1]tim2_ch3/pa3与驱动芯片u6的驱动输入端5b相连;处理器u1的驱动数据端oscout/pa2与驱动芯片u6的驱动输入端6b相连,处理器u1的驱动数据端oscin/pa1与驱动芯片u6的驱动输入端7b相连;

[0064]

驱动芯片u6的驱动输出端4c与风机驱动接口p7的驱动输入第一端相连,驱动芯片u6的驱动输出端5c与风机驱动接口p7的驱动输入第二端相连,驱动芯片u6的驱动输出端6c与风机驱动接口p7的驱动输入第三端相连,驱动芯片u6的驱动输出端7c与风机驱动接口p7

的驱动输入第四端相连,风机驱动接口p7的电源端与+12v电源相连;

[0065]

在本实用新型的一种优选实施方式中,在控制器上还包括风机转速档位设置模块,该风机转速档位设置模块为第一风机转速档位设置模块,第一风机转速档位设置模块包括:如图2、3和11所示,处理器u1的数据输入端[tim1_ch1n]ain0/pb0分别与接口j2的输出第一端、接口j2的输出第二端、接口j2的输出第三端、接口j2的输出第四端、接口j2的输出第五端、接口j2的输出第六端、接口j2的输出第七端和接口j2的输出第八端相连;

[0066]

接口j2的输入第一端分别与电阻组rn10的第一电阻第一端和电阻组rn10的第二电阻第一端相连,接口j2的输入第二端分别与电阻组rn10的第三电阻第一端和电阻组rn10的第四电阻第一端相连,接口j2的输入第三端分别与电阻组rn9的第一电阻第一端和电阻组rn9的第二电阻第一端相连,接口j2的输入第四端分别与电阻组rn9的第三电阻第一端和电阻组rn9的第四电阻第一端相连;

[0067]

接口j2的输入第五端分别与电阻组rn9的第二电阻第二端和电阻组rn9的第三电阻第二端相连,接口j2的输入第六端分别与电阻组rn9的第一电阻第二端和电阻组rn10的第四电阻第二端相连,接口j2的输入第七端分别与电阻组rn10的第二电阻第二端和电阻组rn10的第三电阻第二端相连,接口j2的输入第八端分别与电阻组rn10的第一电阻第二端和+5v电源相连,电阻组rn9的第四电阻第二端与电源地相连。在本实施方式中,接口j2的型号为hdr2x8,电阻组rn9和电阻组rn10中的第一电阻~第四电阻的阻值为10k。其电阻组rn9中的电阻从右往左依次是第一电阻、第二电阻、第三电阻和第四电阻;电阻组rn10中的电阻从右往左依次是第一电阻、第二电阻、第三电阻和第四电阻。

[0068]

在本实用新型的一种优选实施方式中,在控制器上还包括第二风机转速档位设置模块,第二风机转速档位设置模块包括:如图2、3和12所示,处理器u1的数据输入端ain8/pe7分别与接口j3的输出第一端、接口j3的输出第二端、接口j3的输出第三端、接口j3的输出第四端、接口j3的输出第五端、接口j3的输出第六端、接口j3的输出第七端和接口j3的输出第八端相连;

[0069]

接口j3的输入第一端分别与电阻组rn12的第一电阻第一端和电阻组rn12的第二电阻第一端相连,接口j3的输入第二端分别与电阻组rn12的第三电阻第一端和电阻组rn12的第四电阻第一端相连,接口j3的输入第三端分别与电阻组rn11的第一电阻第一端和电阻组rn11的第二电阻第一端相连,接口j3的输入第四端分别与电阻组rn11的第三电阻第一端和电阻组rn11的第四电阻第一端相连;

[0070]

接口j3的输入第五端分别与电阻组rn11的第二电阻第二端和电阻组rn11的第三电阻第二端相连,接口j3的输入第六端分别与电阻组rn11的第一电阻第二端和电阻组rn12的第四电阻第二端相连,接口j3的输入第七端分别与电阻组rn12的第二电阻第二端和电阻组rn12的第三电阻第二端相连,接口j3的输入第八端分别与电阻组rn12的第一电阻第二端和+5v电源相连,电阻组rn11的第四电阻第二端与电源地相连。在本实施方式中,接口j3的型号为hdr2x8,电阻组rn11和电阻组rn12中的第一电阻~第四电阻的阻值为10k。其电阻组rn11中的电阻从右往左依次是第一电阻、第二电阻、第三电阻和第四电阻;电阻组rn12中的电阻从右往左依次是第一电阻、第二电阻、第三电阻和第四电阻。

[0071]

在本实用新型的一种优选实施方式中,在控制器上还包括第三风机转速档位设置模块,第三风机转速档位设置模块包括:如图2、3和13所示,处理器u1的数据输入端ain9/

pe6分别与接口j4的输出第一端、接口j4的输出第二端、接口j4的输出第三端、接口j4的输出第四端、接口j4的输出第五端、接口j4的输出第六端、接口j4的输出第七端和接口j4的输出第八端相连;

[0072]

接口j4的输入第一端分别与电阻组rn14的第一电阻第一端和电阻组rn14的第二电阻第一端相连,接口j4的输入第二端分别与电阻组rn14的第三电阻第一端和电阻组rn14的第四电阻第一端相连,接口j4的输入第三端分别与电阻组rn13的第一电阻第一端和电阻组rn13的第二电阻第一端相连,接口j4的输入第四端分别与电阻组rn13的第三电阻第一端和电阻组rn13的第四电阻第一端相连;

[0073]

接口j4的输入第五端分别与电阻组rn13的第二电阻第二端和电阻组rn13的第三电阻第二端相连,接口j4的输入第六端分别与电阻组rn13的第一电阻第二端和电阻组rn14的第四电阻第二端相连,接口j4的输入第七端分别与电阻组rn14的第二电阻第二端和电阻组rn14的第三电阻第二端相连,接口j4的输入第八端分别与电阻组rn14的第一电阻第二端和+5v电源相连,电阻组rn13的第四电阻第二端与电源地相连。在本实施方式中,接口j4的型号为hdr2x8,电阻组rn13和电阻组rn14中的第一电阻~第四电阻的阻值为10k。其电阻组rn13中的电阻从右往左依次是第一电阻、第二电阻、第三电阻和第四电阻;电阻组rn14中的电阻从右往左依次是第一电阻、第二电阻、第三电阻和第四电阻。

[0074]

在本实用新型的一种优选实施方式中,在控制器上还包括风机转速档位显示模块,该风机转速档位显示模块为第一风机转速档位显示模块,第一风机转速档位显示模块包括:如图2、3和14所示,处理器u1的数据端pd4(hs)/tim2_ch1[beep]与电阻r25的第一端相连,电阻r25的第二端与显示驱动芯片u8的数据端din相连,显示驱动芯片u8的电源端vdd分别与+5v电源和电容c27的第一端相连,显示驱动芯片u8的电源地端gnd分别与电源地和电容c27的第二端相连;

[0075]

显示驱动芯片u8的七段数据端a与七段数码管led2的七段数据端a相连,显示驱动芯片u8的七段数据端b与七段数码管led2的七段数据端b相连,显示驱动芯片u8的七段数据端c与七段数码管led2的七段数据端c相连,显示驱动芯片u8的七段数据端d与七段数码管led2的七段数据端d相连,显示驱动芯片u8的七段数据端e与七段数码管led2的七段数据端e相连,显示驱动芯片u8的七段数据端f与七段数码管led2的七段数据端f相连,显示驱动芯片u8的七段数据端g与七段数码管led2的七段数据端g相连,显示驱动芯片u8的数据点端h与七段数码管led2的数据点端dp相连,显示驱动芯片u8的公共端gr0与七段数码管led2的公共端com相连。在本实施方式中,显示驱动芯片u8的型号为tm3130,七段数码管led2采用0.39英寸共阳极数码管,电阻r25的阻值为100ω,电容c27的容值为0.1uf。

[0076]

在本实用新型的一种优选实施方式中,在控制器上还包括第二风机转速档位显示模块,第二风机转速档位显示模块包括:如图2、3和14所示,显示驱动芯片u8的七段数据端a与七段数码管led3的七段数据端a相连,显示驱动芯片u8的七段数据端b与七段数码管led3的七段数据端b相连,显示驱动芯片u8的七段数据端c与七段数码管led3的七段数据端c相连,显示驱动芯片u8的七段数据端d与七段数码管led3的七段数据端d相连,显示驱动芯片u8的七段数据端e与七段数码管led3的七段数据端e相连,显示驱动芯片u8的七段数据端f与七段数码管led3的七段数据端f相连,显示驱动芯片u8的七段数据端g与七段数码管led3的七段数据端g相连,显示驱动芯片u8的数据点端h与七段数码管led3的数据点端dp相连,

显示驱动芯片u8的公共端gr1与七段数码管led3的公共端com相连。在本实施方式中,七段数码管led3采用0.39英寸共阳极数码管。

[0077]

在本实用新型的一种优选实施方式中,在控制器上还包括第三风机转速档位显示模块,第三风机转速档位显示模块包括:如图2、3和14所示,显示驱动芯片u8的七段数据端a与七段数码管led4的七段数据端a相连,显示驱动芯片u8的七段数据端b与七段数码管led4的七段数据端b相连,显示驱动芯片u8的七段数据端c与七段数码管led4的七段数据端c相连,显示驱动芯片u8的七段数据端d与七段数码管led4的七段数据端d相连,显示驱动芯片u8的七段数据端e与七段数码管led4的七段数据端e相连,显示驱动芯片u8的七段数据端f与七段数码管led4的七段数据端f相连,显示驱动芯片u8的七段数据端g与七段数码管led4的七段数据端g相连,显示驱动芯片u8的数据点端h与七段数码管led4的数据点端dp相连,显示驱动芯片u8的公共端gr2与七段数码管led4的公共端com相连。在本实施方式中,七段数码管led4采用0.39英寸共阳极数码管。

[0078]

在本实用新型的一种优选实施方式中,在控制器上还包括显示屏数据采集模块,显示屏数据采集模块包括:如图2、3和15所示,处理器u1的显示屏数据采集端[tim1_ch2n]ain1/pb1分别与电阻r24的第一端、电阻r26的第一端和电容c23的第一端相连,电阻r24的第二端分别与电容c22的第一端和接口j8输出端相连,接口j8接地端与电源地相连,电容c22的第二端、电容c23的第二端和电阻r26的第二端分别与电源地相连。在本实施方式中,电阻r24、电阻r26的阻值为10k,电容c22、电容c23的容值为0.1uf,接口j8采用的型号为hdr1x4。

[0079]

在本实用新型的一种优选实施方式中,在控制器上还包括风机脉冲数设置模块,风机脉冲数设置模块包括:如图2、3和16所示,处理器u1的数据端pg0分别与电阻组rn7的第一电阻第一端和开关组sw1的第一开关第一端相连,处理器u1的数据端pg1分别与电阻组rn7的第二电阻第一端和开关组sw1的第二开关第一端相连,处理器u1的数据端pe3/tim1_bkin分别与电阻组rn7的第三电阻第一端和开关组sw1的第三开关第一端相连,处理器u1的数据端pe0(hs)/clk_cco分别与电阻组rn7的第四电阻第一端和开关组sw1的第四开关第一端相连,处理器u1的数据端pe1(t)/i2c_scl分别与电阻组rn8的第三电阻第一端和开关组sw1的第五开关第一端相连,处理器u1的数据端pe2(t)i2c_sda分别与电阻组rn8的第四电阻第一端和开关组sw1的第六开关第一端相连;

[0080]

电阻组rn7的第一电阻第二端、电阻组rn7的第二电阻第二端、电阻组rn7的第三电阻第二端、电阻组rn7的第四电阻第二端、电阻组rn8的第三电阻第二端、电阻组rn8的第四电阻第二端分别与电源地相连;

[0081]

开关组sw1的第一开关第二端、开关组sw1的第二开关第二端、开关组sw1的第三开关第二端、开关组sw1的第四开关第二端、开关组sw1的第五开关第二端和开关组sw1的第六开关第二端分别与电源地相连。在本实施方式中,开关组sw1的型号为dmr-06-v-t/r,电阻组rn7和电阻组rn8中的第一电阻~第四电阻的阻值为100k。其开关组sw1中的开关从上到下依次是第一开关、第二开关、第三开关、第四开关、第五开关和第六开关;电阻组rn7中的电阻从上到下依次是第一电阻、第二电阻、第三电阻和第四电阻,电阻组rn8中的电阻从上到下依次是第一电阻、第二电阻、第三电阻和第四电阻。

[0082]

在本实用新型的一种优选实施方式中,在控制器上还包括spi接口模块,spi接口

包括:如图2、3和17所示,处理器u1的spi数据时钟端pc5(hs)/spi_sck与spi接口j5的时钟端相连,处理器u1的spi数据端pc6(hs)/spi_mosi与spi接口j5的数据端相连;spi接口j5的电源端与+5v电源相连,spi接口j5的电源地端与电源地相连。在本实施方式中,未给出处理器u1与spi接口j5的整个连接,只给出了部分连接。

[0083]

尽管已经示出和描述了本实用新型的实施例,本领域的普通技术人员可以理解:在不脱离本实用新型的原理和宗旨的情况下可以对这些实施例进行多种变化、修改、替换和变型,本实用新型的范围由权利要求及其等同物限定。

起点商标作为专业知识产权交易平台,可以帮助大家解决很多问题,如果大家想要了解更多知产交易信息请点击 【在线咨询】或添加微信 【19522093243】 与客服一对一沟通,为大家解决相关问题。

与客服一对一沟通,为大家解决相关问题。

此文章来源于网络,如有侵权,请联系删除

热门咨询

热门咨询

tips

商标分类

商标分类  商标转让

商标转让